大家好、

共享的国际中继器项目目前使用 AFE7769 (4T4R2FB)和 SN18064 (4T4R1FB)。 SN18064的通道3/4存在问题

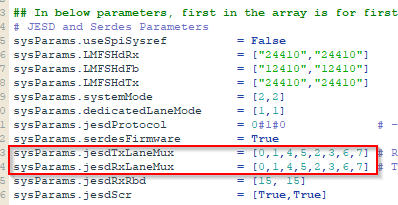

- SN18064的问题:它处于4TR 双同步模式下(通道1/2发送和接收2个同步;通道3/4发送和接收2个同步)。 通道1/2正常。 通道3/4传输通道的同步可以被拉高,但没有信号输出。 通道3/4接收到的 SYNC 始终为低电平。

1) 1)对于通道3/4的接收通道、在 FPGA 数据采集中看不到 lane3的 K 代码。

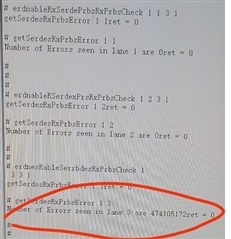

2) 2) FPGA 发送 PRBS 代码并使用 TI 的 K C 函数中的算法来检查每个通道的错误。 发现通道3中有许多错误、如下所示:

3) 3)在 FPGA 侧、Gty 执行回送、SYNC 引脚同时环回。 4个通道可以顺利发送和接收数据、数据正常、同步可被拉至高电平。

4) 4) FPGA 外部的跳线环回与 lane3对应的 Gty。 由于跳线、速度无法达到10G、并降至2.5G。 在 ibert 上、PRBS 看起来正常。

因此、我认为当 SN18064配置 lane3时出现了问题。 请帮我找到问题发生的位置吗? 提前感谢您。

此致、

凯瑟琳