您好!

我使用的配置如下:

LMFSHdTx[14810]和 LMFSHdRx [181610]

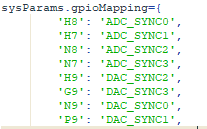

SYNC_IN 用于连接 LVDS 和 H8以及 H7引脚。 (SYNC_IN0)

SYNC_IN1 (N8和 N7)引脚未连接。

SYNC_OUT 连接 LVDS、N9和 P9引脚。 (SYNC_OUT1)

SYNC_OUT0 (H9和 G9)引脚未连接。

GPIO 引脚连接 GPIO1….GPIO6。

但是、 我无法使同步信号正常工作。 Latte 启动文件如下所示:

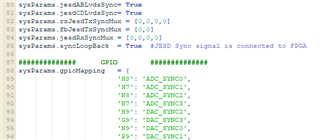

###以下参数设置 SYNCIN 和 SYNCOUT 以与 TSW14J57连接

sysParams.jesdABLvdsSync = 1.

sysParams.jesdCDLvdsSync = 1.

sysParams.rxJesdTxSyncMux =[0、0、0、0]

sysParams.fbJesdTxSyncMux =[0、0]

sysParams.jesdRxSyncMux =[0、0、0、0]#[0、0、1、1]

sysParams.syncLoopBack =真

我应该如何设置这个位置、以便同步信号从我指定的引脚工作?

谢谢、