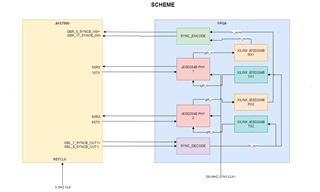

图1.

我拥有采用 AFE7900和 Xilinx Xcku050 FPGA 的定制电路板设计。

图1显示 了我的设计中的 FPGA-AFE 连接。

所有 Xilinx JESD204 IP 均配置为 LMFS=1-4-8-1-0、K=4、LaneRate =10Gbps。 core_clk 频率为250MHz。

我想配置 AFE7900 2-link 1-4-8-1-0配置。 通道速率为10Gbps。

FPGA 启动后、 将在 Latte Scripts 中创建配置步骤。 (它位于附加文件中。)

我在 ILA 中检查 Xilinx IP gt0_Rx 信号、但我在 gt0_Rx 信号中没有看到 h'BCBCBCBCBCBCBCBCBCBCBCBCBC。

因此、FPGA RX IP 无法完成同步过程。

为什么 FPGA 没有在 SERDES 线路中捕获 h'BCBCBCBCBCBCBCBCBCBCBBC 字符?

我不知道如何调试它。

您能就此问题向我提供建议吗?

此致。

Stsecen