主题中讨论的其他器件: TI-JESD204-IP、 AFE7950

AFE7950EVM 能否在 Xilinx ZC706上运行?

我想使用 LabVIEW 和 Vivado 开发程序。 我已经获得了 TI-JESD204-IP、但不知道如何启动。

TI 能否提供库和用途?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

AFE7950EVM 能否在 Xilinx ZC706上运行?

我想使用 LabVIEW 和 Vivado 开发程序。 我已经获得了 TI-JESD204-IP、但不知道如何启动。

TI 能否提供库和用途?

高朝阳

您是否有权访问 AFE79xx 安全文件夹? 我们有一个现有设计、该设计使用适用于 AFE79xx 和 Xilinx ZCU102的 TI-JESD204-IP。 您可以将其用作参考。

AFE7950EVM 还可与 ZC706搭配使用。 我们可能已经有了 ZC706的示例设计。 我将与从事此工作的工程师核实、看看我们是否可以向您提供此信息。

此致、

Vijay

LiehChun、您好!

该安全文件夹最近才更新为具有 ZC706参考设计、因此如果您之前下载了文件、您可能没有该项目。 请访问您被授予访问权限的 AFE79xx 安全文件夹、您可以下载 zc706参考设计。 您可以通过此链接https://www.ti.com/securesoftware/访问该文件夹、 并需要登录您的 myTI 帐户。

(笑声)

此致、

David Chaparro

您好 David,

谢谢您的建议。 我已经下载并检查了 ZC706示例。 它可以由 Vivado 实现。

我检查了设计原理图文件、找到了链接到 FT4232H 的 SPIB1和 SPIB2。 看起来 SPI 命令是通过 FT4232H 从 USB 传输到 SPI 的。 是否有任何包含寄存器初始化或配置的文件?

示例不是 Vivado 项目。 我没有通过7系列 FPGA 收发器向导看到配置。 如何配置 GTX 线?

高朝阳

样本数应设置为1024、因为这是在 Vivado 的 ILAS 中捕获的样本数。 为了查看全部4个 Rx 通道、我建议遵循 TI204c-Setup 文档中提到的设置。

安全文件夹中提供的参考设计未使用 FB 通道、因此无法捕获 FB 数据。 如果需要 FB 通道、则需要更新 Latte 脚本和 Vivado 参考设计。 在 Latte 中、需要正确启用/设置 FB 通道、并且需要更新 Vivado 项目以匹配新的 AFE 设置。

此致、

David Chaparro

尊敬的 David:

我不确定该怎么办。

这话什么意思

修改 JESD_LINK_params.VH `deFine NUMBER_OV_RX_Lanes 12.

修改 refdesign_rx.SV、 添加 assign fb1_I_samples[i]= rx_lane 数据[8][63-16*i -:adc_res];

分配 fb1_Q_samples[i]= rx_lane 数据[9][63-16*i -:adc_Res];

分配 fb2_i_samples[i]= rx_lane 数据[10][63-16*i -:adc_Res];

分配 fb2_Q_samples[i]= rx_lane 数据[11][63-16*i -:adc_Res];

我是否需要修改 constrainations.XDC 或其他文件?

高朝阳

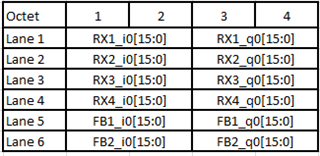

AFE79xx 器件只有8个 STX 通道、可供 Rx 和 FB 通道使用。 这意味着必须更新 AFE79xx 配置、以便 Rx 和 FB 通道共享8个通道。 一种方法是将 Rx LMFS 模式更新为24410、将 FB LMFS 更新为12410。 这会将 Rx 和 FB 通道配置为总共使用6个通道。 然后、您可以更新 JESD_LINK_params、refdesign_Rx 和收发器 IP 以使用6个通道。 对于 refdesign_Rx 文件、需要为 Rx 和 FB 更新数据解压缩、因为现在 LMFS 为24410或12410、数据格式将为:

为我提到的模式配置的 Latte 脚本如下所示。

e2e.ti.com/.../TI_5F00_IP_5F00_10Gbps_5F00_4T4R2F_5F00_ConfigLmk.py

此致、

David Chaparro