主题中讨论的其他器件: AFE7950

我想在 HTG-Z920上运行 AFE7950EVM。

我有 ZC706的参考设计、但 GTX_8b10b_rxtx IP 不受支持。

TI 能否提供 HTG-Z920 (CORE:Xilinx Zynq UltraScale+ ZU19-L2 xczu19eg-ffvc1760-2-e )的参考?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我想在 HTG-Z920上运行 AFE7950EVM。

我有 ZC706的参考设计、但 GTX_8b10b_rxtx IP 不受支持。

TI 能否提供 HTG-Z920 (CORE:Xilinx Zynq UltraScale+ ZU19-L2 xczu19eg-ffvc1760-2-e )的参考?

尊敬的 David:

我想在 HTG-Z920上运行 ZC706的4T4R2F 参考设计。

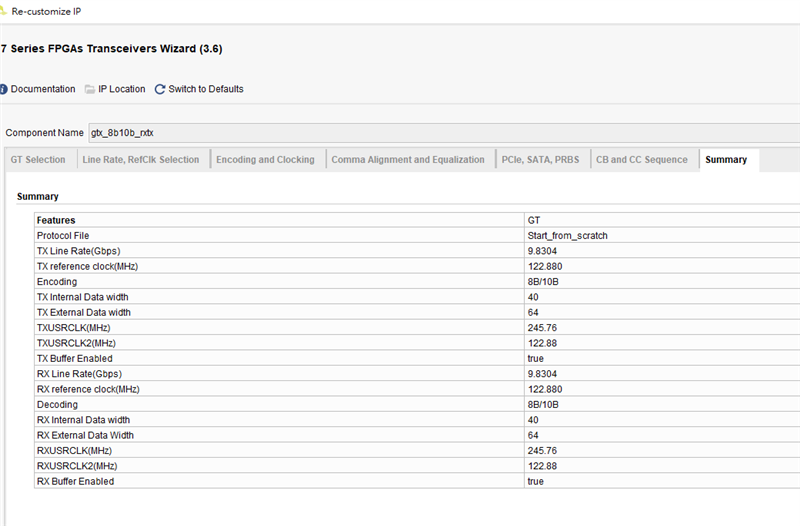

ZC706收发器向导摘要如下图所示。

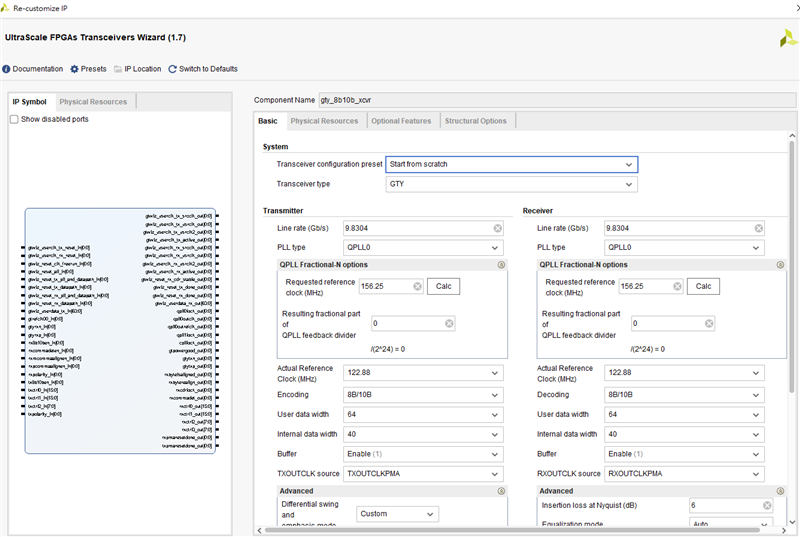

我想修改 vcu118 参考设计以满足我的目标。

我将线路速率修改为9.8304、请求的参考时钟修改为122.88、实际 的参考时钟修改为122.88、自由运行的 DRP 时钟频率修改为122.88。

当重新打开收发器向导时、 请求的参考时钟会改回156.25。

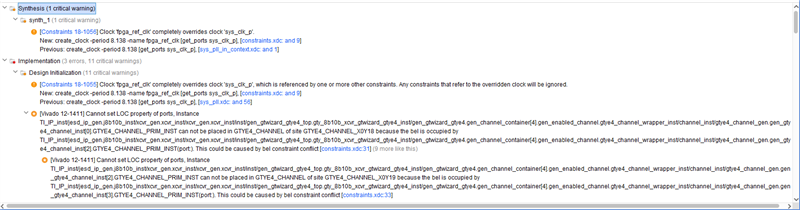

Vivado 在编译时显示错误。

我应该怎么做?

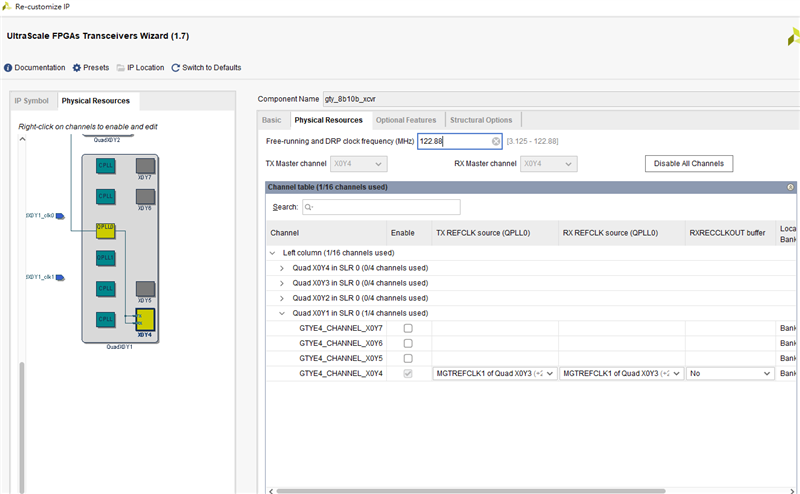

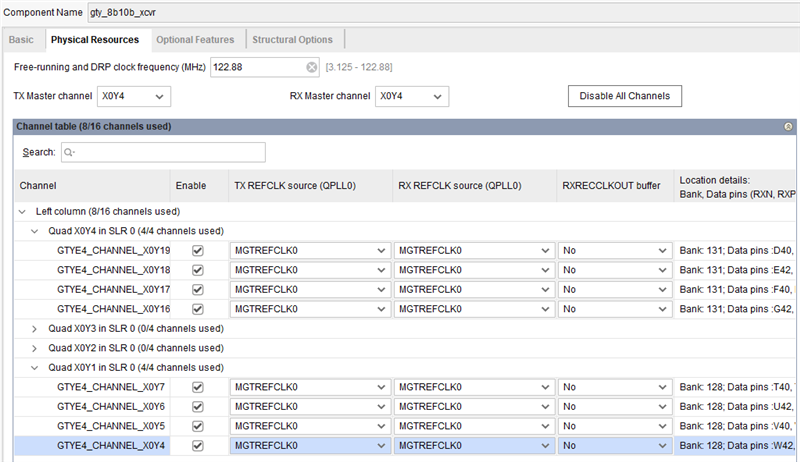

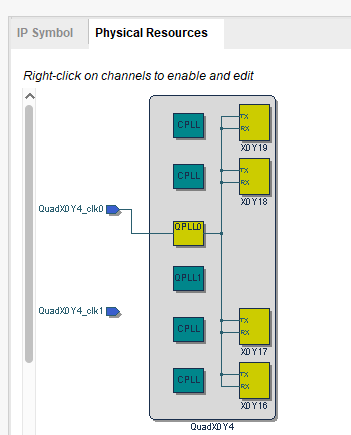

我启用如下通道。

我在.XDC 中添加了引脚位置、针对 4T4R2FB 模式更新了 JESD_LINK_params.VH、并使用122.88MHz 更新了 SYS_PLL。

Vivado 显示了一些错误。

[vivado 12-1411]无法设置端口的 LOC 属性、例如 TI_IP_inst/JESD_IP_gen.j8b10b_inst/xcvr_inst/xcvr_inst/xcvr_inst/gen_ip_inst/gtty4_top.gtvr_gvr_inst_g4、因为它不能在 tchannel_g4通道中启用 这可能是由 bel 约束冲突引起的["C:/X/vcu118_8b10b/source/constraints.xdc:33]

[Place 30-739] IBUFDS_GT/GT / GT 组件对的次优布局。如果此次优条件对于此设计是可以接受的、则可以使用.xdc 文件中的 clock_ded专用_route 约束将此消息降级为警告。 但是、强烈建议不要使用此覆盖。 这些示例可直接在.xDC 文件中使用、以覆盖此时钟规则。

< SET_PROTIVE_CLOSE_PROJECT_route false [get_nets TI_IP_inst/JESD_IP_gen.j8b10b_inst/xcvr_gen.xcvr_inst/gt_refclk0_BUf]>

TI_IP_inst/JESD_IP_gen.j8b10b_inst/xcvr_gen.xcvr_inst/genblk1[0].IBUFDS_GTE4_INST (IBUFDS_GTE4.O)锁定到 GTYE4_common_X0Y4

TI_IP_INST/JESD_IP_gen.j8b10b_inst/xcgen_gen.xcvr_inst/xcvr/inst/inst/gtwizard_gtye4_top.Gty_8b10b_xcvr_inst_gcyvr_gtye4_inst_inst_gtwizard_gty_g4_gcommon.gprison_gte4_gprison_gpring_gprison_gprison_g4 g4 g4 gtegrgest_gest_g4 g4 g4 gtegrg4 g4 gtegrgest_common_gest_gest_g4 g4 g4 gest_common_gest_gest_gest_gest_gest_gest_gest_g4 gtegrg4 g4

上述错误可能与其他连接的实例有关。 以下是的列表

所有相关的时钟规则及其各自的实例。

将检查 XDC 中的位置。 没关系。

我还应该做什么?

高朝阳

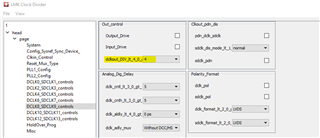

要更改 LMK 设置、您可以从 Latte 软件右侧的器件列表中选择"LMK 时钟分频器"。 这将打开另一个窗口、您可以 在其中更新 DCLK9的分频系数、如下所示。

要读回 LMK 设置、您必须首先将 LMK 读出模式更改为3 线 SPI。 为此、您必须转到"View"选项卡并选择"View RegProgrammer"、然后您可以将读出模式更改为3线 SPI。 现在、当您右键单击某个设置并按"获取值"时、您可以读回正确的值。

此致、

David Chaparro