请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE7900EVM 大家好!

我想使用 FPGA 向 DAC 发送数据、据我所知、我需要向 FPGA 发送一个复位信号、表明我的链路已设置、允许 FPGA 发送数据。

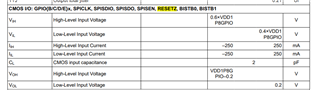

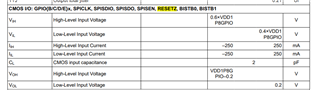

我在数据表中找到了 resetZ、但这似乎是输入信号?具有 FMC 的 RESET_FPGA 接口似乎不起作用。

我在下面附上了相关的图片,希望我能得到一些答案

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好!

我想使用 FPGA 向 DAC 发送数据、据我所知、我需要向 FPGA 发送一个复位信号、表明我的链路已设置、允许 FPGA 发送数据。

我在数据表中找到了 resetZ、但这似乎是输入信号?具有 FMC 的 RESET_FPGA 接口似乎不起作用。

我在下面附上了相关的图片,希望我能得到一些答案