主题中讨论的其他器件: AFE7769、 AFE7769EVM、TSW14J58EVM

您好、

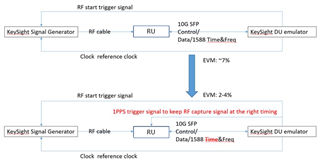

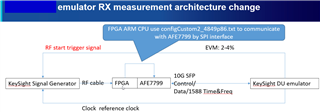

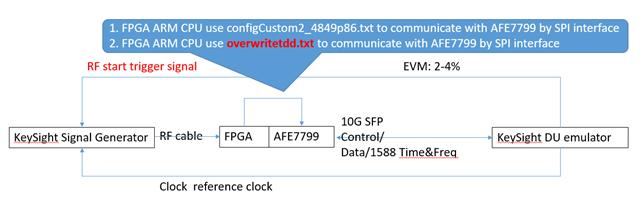

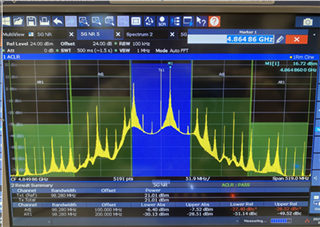

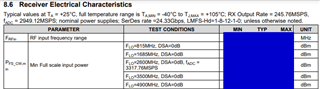

客户在其电路板上测量了 AFE7799的 Rx EVM、结果显示超过了2.5%。 您会不会建议改进 Rx EVM 的可能方法?

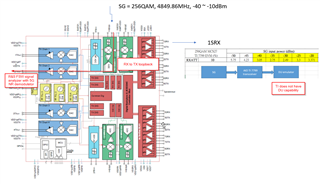

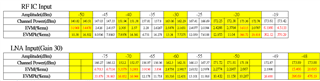

|

256QAM |

SG 输入功率(dBm) |

||||||||

|

-50 |

-45 |

-40 |

-35 |

-30 |

-25 |

-20 |

|

||

|

RXATT |

10 |

5.75 |

4.23 |

3.05 |

2.75 |

2.49 |

3.3 |

3.371 |

|

谢谢。

阿兰