主题中讨论的其他器件: AFE7950、 LMK04828、LMK04832

您好!

客户希望为 AFE7950EVM 中的抖动清除器使用外部时钟源。

您能为该申请提供指导吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

客户希望为 AFE7950EVM 中的抖动清除器使用外部时钟源。

您能为该申请提供指导吗?

尊敬的 Byungsoo:

很抱歉耽误你的时间。

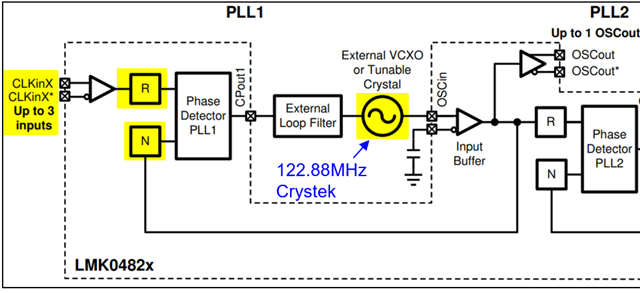

如果您说要向抖动清除器输入时钟、我假设您要在双 PLL 模式下使用 LMK04828、在这种模式下、PLL1用作抖动清除器、而不是为其提供在分配模式下使用的时钟。 如果正确、则必须设置以下参数、以便包含以下公式:

FIN/R = 122.88/N

由于下图中的相位检测器:

您可以在 AFE79xx GUI 中更改 R 和 N 分频器值、方法是根据所需的 Fin.

lmk 头页 PLL1_Config.Clkin0_1_2_Divider.div_clkin1_lt_13_0_gt_= R

lmk.head.page.PLL1_Config.N_Divider_PLL1.N_DIV_PLL1_lt_13_0_gt_= N

并且确保 lmkParams.pllEn = True

此致!

卡米洛

尊敬的 Byungsoo:

如果您的目标是将 LMK04828的输入从板载振荡器更改为 PLL2的外部时钟、则 EVM 的设计并不支持此选项。 因为 OSCin 引脚仅连接到板载振荡器。 如果您确实想执行类似操作、可能有三个选项:

我们将根据您选择的选项提供更多指导。

此致!

卡米洛

尊敬的 Byungsoo:

好的。 为此、您的启动脚本必须相应地设置以下参数:

您好,Camilo,

我在 Latte 中修改脚本

请检查下面的脚本。

谢谢你。

############################## Read me ####################

#使用外部时钟而不是板载时钟。 而 LMK04832在分配模式下工作。

在 HSDC Pro DAC 选项卡中、选择 AFE79xx_2x2TX_44210;数据速率= 491.52M

#在 HSDC Pro ADC 选项卡中,选择 AFE79xx_2x2RX_24410;数据速率= 245.76M -->以采集4个 RX 通道

#在 HSDC Pro ADC 选项卡中,选择 AFE79xx_1x2FB_44210;数据速率= 491.52M -->以捕获2个 FB 通道

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 #使用 HSDC Pro 设置 FPGA (TSW14J56)

############################## 顶级######################

sysParams。 FRef = 491.52

sysParams。 FadcRx = 2949.12

sysParams。 FadcFb = 2949.12

sysParams。 Fdac = 2949.12*4

sysParams.externalClockRx=错误

sysParams.externalClockTx=错误

############################## 数字链########################

#### 处方####

sysParams.ddcFactorRx =[12、12、12]# RX A、B、C 和 D 的 DDC 抽取因子

sysParams.rxNco0 =[[5,320,5320 ]、#Band0、Band1表示 RXA

[5,320,5320 ]、#Band0、Band1表示 RXB

[5,320,5320 ]、#Band0、Band1表示 RXC

[5320 5320]]# RXD 的 Band0、Band1

#### FB ####

sysParams.ddcFactorFb =[6、6]# FB 1和2的 DDC 抽取因子

sysParams.fbNco0 =[5,320,5320 ]#Band0 (对于 FB1和 FB2)

#### 发送####

sysParams.ducFactorTx =[24、24、24]# TX A、B、C 和 D 的 DUC 内插因子

sysParams.txNco0 =[5,400,5400]、#Band0、Band1 (对于 TXA)

[5,400,5400]、#Band0、Band1 (对于 TXB)

[5,400,5400]、#Band0、Band1 (对于 TXC)

[5,400,5400]]# TXD 的 Band0、Band1

############################## JESD ########################

#### ADC-JESD ####

sysParams.jesdSystemMode=[1,1]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; Rx -Rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb - fb- fb - fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol=[0,0]# 0 - 8b/10b 编码;2 - 64b/66b 编码

sysParams。 LMFSHdRx =["24410"、"24410"、"24410"、"24410"]

#第2个和第4个值仅对 jesdSystemMode 中的值有效(0,2)。

#对于其他模式,请为第1和第3选择4个转换器模式。

sysParams。 LMFSHdFb =["22210"、"22210"]

sysParams.rxJesdTxScr =[真、真、真、真]

sysParams.fbJesdTxScr =[True、True]

sysParams.rxJesdTxK =[16、16、16、16]

sysParams.fbJesdTxK =[16,16]

sysParams.jesdTxLaneMux =[0、1、2、3、4、5、6、7]#输入您要在每个位置使用的通道。

#例如,如果你想交换每2T 的前两行,

#这应该是[1,,0,2,3],[5,4,6,7]]

#### DAC-JESD ####

sysParams.jesdRxProtocol=[0、0]

sysParams。 LMFSHdTx =["44210"、"44210"、"44210"、"44210"]

sysParams.jesdRxLaneMux =[0、1、2、3、4、5、6、7]#输入您要在每个位置使用的通道。

#例如,如果您要交换每个2R 的前两行

#这应该是[1,,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd =[4、4]

sysParams.jesdRxScr =[真、真、真、真]

sysParams.jesdRxK =[16、16、16]

#### JESD 通用####

sysParams.jesdABLvdsSync= True

sysParams.jesdCDLvdsSync= True

sysParams.syncLoopBack = True #JESD 同步信号已连接到 FPGA

############################## GPIO ##############################

sysParams.gpioMapping ={

'H8':'ADC_SYNC0'、

'H7':'ADC_SYNC1'、

'N8':'ADC_SYNC2'、

'N7':'ADC_SYNC3'、

'h9':'DAC_SYNC0'、

'G9':'DAC_SYNC1'、

'n9':'DAC_SYNC2'、

'P9':'DAC_SYNC3'、

'P14':'GLOBAL_PDN'、

'K14':'FBABTDD'、

'R6':'FBCDTDD'、

'H15':['TXATDD'、'TXBTDD']、

'V5':['TXCTDD'、'TXDTDD']、

'E7':['RXATDD'、'RXBTDD']、

'R15':['RXCTDD'、'RXDTDD']}

############################## LMK 参数####################

lmkParams.pllEn =假

lmkParams.inputClk = 491.52 #仅当 lmkParams.pllEn = False 时有效

lmkParams.lmkFrefClk =真

对于 TSW14J56、setupParams.fpgaRefClk = 245.76#应等于 LaneRate/40

############################## 记录##########################

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x0 #Modify to 0x1以将寄存器序列保存至日志文件。 执行脚本需要更多时间。

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

#------------------ #

AFE.deviceBringup ()

AFE.TOP.overrideTdd (15、3、15)#位元;4R、2F、4T

您好,Camilo,

今天、我按如下方式进行测试:

1.为 LMK_CLK_IN 将外部100 MHz 时钟连接到 EVM 上的 J14。

2.执行高速数据转换器专业版

3.执行 Latte。

4.在高速数据转换器专业版的250MHz 抽头上将数据速率设置为 DAC。

5.设置其他设置进行测试。

6.按发送按钮。

7.我提出按照 Latte 指南。

8.运行修改的 python 脚本。

Latte 消息输出如"SPIA 拥有 PLL 页面的控制权

PLL 未锁定"。

下面的添加了修改后的 python 脚本。 测试此消息并记录 Latte 输出消息日志。

请在下面查看附加的 python 脚本和 Latte 输出消息。

请告诉我犯了什么错误。

谢谢你。

---------------- python 脚本的开头-------------------------------------------------------

############################## Read me ####################

#使用外部时钟而不是板载时钟。 而 LMK04832在分配模式下工作。

在 HSDC Pro DAC 选项卡中、选择 AFE79xx_2x2TX_24410;数据速率= 250m

#在 HSDC Pro ADC 选项卡中、选择 AFE79xx_2x2RX_24410;数据速率= 250m -->以采集4个 RX 通道

#在 HSDC Pro ADC 选项卡中、选择 AFE79xx_1x2FB_24410;数据速率= 250m -->以采集2个 FB 通道

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 #使用 HSDC Pro 设置 FPGA (TSW14J56)

############################## 顶级######################

sysParams。 FRef = 250

sysParams。 FadcRx = 6000

sysParams。 FadcFb = 6000

sysParams。 Fdac = 12000

sysParams。 RRFMode = 5 #RRFMode 0:4T4R2F FDD 模式

#RRFMode 1:4T4R1F FDD 模式

#RRFMode 2:4T4R2F FDD 模式四频带

#RRFMode 5:4T4R2F TDD 非共享

#RRFMode 6:4T4R1F TDD 非共享

#RRFMode 7:4T4R2F TDD 共享

#RRFMode 8:4T4R1F TDD 共享

#RRFMode 10:2T2R1F TDD AB / 2T2R1F FDD CD

#RRFMode 11: 2T2R1F FDD AB / 2T2R1F TDD CD

sysParams.externalClockRx=错误

sysParams.externalClockTx=错误

############################## 数字链########################

#### 处方####

sysParams.ddcFactorRx =[24、24、24]# RX A、B、C 和 D 的 DDC 抽取因子

sysParams.rxNco0 =[5,400,5400]、#Band0、Band1 (对于 RXA)

[5,400,5400]、#Band0、Band1 (对于 RXB)

[5,400,5400]、#Band0、Band1 (对于 RXC)

[5,400,5400]]# RXD 的 Band0、Band1

#### FB ####

sysParams.ddcFactorFb =[24、24]# FB 1和2的 DDC 抽取因子

sysParams.fbNco0 =[5,400,5400]#Band0 (对于 FB1和 FB2)

#### 发送####

#sysParams.ducFactorTx =[24、24、24]# TX A、B、C 和 D 的 DUC 内插因子

sysParams.ducFactorTx =[48、48、48、48]# TX A、B、C 和 D 的 DUC 内插因子

sysParams.txNco0 =[5,400,5400]、#Band0、Band1 (对于 TXA)

[5,400,5400]、#Band0、Band1 (对于 TXB)

[5,400,5400]、#Band0、Band1 (对于 TXC)

[5,400,5400]]# TXD 的 Band0、Band1

############################## JESD ########################

#### ADC-JESD ####

sysParams.jesdSystemMode=[1,1]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; Rx -Rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb - fb- fb - fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol=[0,0]# 0 - 8b/10b 编码;2 - 64b/66b 编码

sysParams。 LMFSHdRx =["24410"、"24410"、"24410"、"24410"]

#第2个和第4个值仅对 jesdSystemMode 中的值有效(0,2)。

#对于其他模式,请为第1和第3选择4个转换器模式。

sysParams。 LMFSHdFb =["24410"、"24410"]

sysParams.rxJesdTxScr =[真、真、真、真]

sysParams.fbJesdTxScr =[True、True]

sysParams.rxJesdTxK =[16、16、16、16]

sysParams.fbJesdTxK =[16,16]

sysParams.jesdTxLaneMux =[0、1、2、3、4、5、6、7]#输入您要在每个位置使用的通道。

#例如,如果你想交换每2T 的前两行,

#这应该是[1,,0,2,3],[5,4,6,7]]

#### DAC-JESD ####

sysParams.jesdRxProtocol=[0、0]

sysParams。 LMFSHdTx =["24410"、"24410"、"24410"、"24410"]

sysParams.jesdRxLaneMux =[0、1、2、3、4、5、6、7]#输入您要在每个位置使用的通道。

#例如,如果您要交换每个2R 的前两行

#这应该是[1,,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd =[4、4]

sysParams.jesdRxScr =[真、真、真、真]

sysParams.jesdRxK =[16、16、16]

#### JESD 通用####

sysParams.jesdABLvdsSync= True

sysParams.jesdCDLvdsSync= True

sysParams.syncLoopBack = True #JESD 同步信号已连接到 FPGA

############################## GPIO ##############################

sysParams.gpioMapping ={

'H8':'ADC_SYNC0'、

'H7':'ADC_SYNC1'、

'N8':'ADC_SYNC2'、

'N7':'ADC_SYNC3'、

'h9':'DAC_SYNC0'、

'G9':'DAC_SYNC1'、

'n9':'DAC_SYNC2'、

'P9':'DAC_SYNC3'、

'P14':'GLOBAL_PDN'、

'K14':'FBABTDD'、

'R6':'FBCDTDD'、

'H15':['TXATDD'、'TXBTDD']、

'V5':['TXCTDD'、'TXDTDD']、

'E7':['RXATDD'、'RXBTDD']、

'R15':['RXCTDD'、'RXDTDD']}

############################## LMK 参数####################

lmkParams.pllEn =假

lmkParams.inputClk = 250 #仅当 lmkParams.pllEn = False 时有效

lmkParams.lmkFrefClk =真

对于 TSW14J56、setupParams.fpgaRefClk = 250 #应等于 LaneRate/40

############################## 记录##########################

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x0 #Modify to 0x1以将寄存器序列保存至日志文件。 执行脚本需要更多时间。

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

#------------------ #

AFE.deviceBringup ()

AFE.TOP.overrideTdd (15、3、15)#位元;4R、2F、4T

---------------- python 脚本结尾-------------------------------------------------------

---------------- Latte 输出消息的开始-------------------------------------------------------

#正在执行.. AFE7950/bringup/S8_ExternalClk_RX_250m_TX_FB_250m_center_care.py 5400MHz

#开始时间2024年02月13日19:50:47.569000

对于这些速率、不支持1KHz 光栅模式。 更改为32位 NCO 模式。

外部 Sysref 频率应为以下的整数因子:3.90625MHz

2T2R1F 编号:0

有效配置:true

laneRateRx:10000.0

laneRateFb:10000.0

laneRateTx:10000.0

2T2R1F 编号:1

有效配置:true

laneRateRx:10000.0

laneRateFb:10000.0

laneRateTx:10000.0

ChipVersion 的器件初始化:1.3

LMK 时钟分频器-器件寄存器复位。

LMK 时钟分频器-器件寄存器复位。

donot_open_Atharv_full -器件寄存器复位。

芯片类型:0xA

芯片 ID:0x78

芯片版本:0x11

SPIA 可以控制 PLL 页面

释放 PLL Pages SPI 控制。

熔丝组负载自动加载成功完成

无自动加载错误

熔丝组负载自动加载成功完成

无自动加载错误

//固件版本=11000

// PG 版本= 1

//发布日期[dd/mm/yy]= 10/7/19

patchSize=11697

//补丁版本= 165

// PG 版本= 0

//发布日期[dd/mm/yy]= 27/11/21

SPIA 可以控制 PLL 页面

PLL 未锁定

#Error:异常必须是旧式类或从 BaseException 而不是 NoneType 派生

#"AFE7950/bringup/S8_ExternalClk_RX_250m_TX_FB_250m_center_cpy.py" 5400MHz、第128行、

#文件"C:\Users\O21027\Documents\Texas Instruments\Latte\lib\\AFE79xxLibraries\\AFE79xxLibraryPG1p0\resourceFiles\mFuncDecorator.py"、在 inDecorator 中、第88行

# a=func(*args,**kwargs)

#文件"C:\Users\O21027\Documents\Texas Instruments\Latte\lib\\AFE79xxLibrary\\AFE79xxLibraryPG1p0\mAfeLibrary.py"、第290行、位于 deviceBringup。

# self.top.configurePll()

#文件"C:\Users\O21027\Documents\Texas Instruments\Latte\lib\\AFE79xxLibraries\\AFE79xxLibraryPG1p0\resourceFiles\mFuncDecorator.py"、在 inDecorator 中、第88行

# a=func(*args,**kwargs)

#文件"C:\Users\O21027\Documents\Texas Instruments\Latte\lib\\AFE79xxLibraryPG1p0\mTopLib.py"、第710行、在 configurePll 中

#提升

#类型错误:异常必须是旧式类或从 BaseException 而不是 NoneType 派生

#

#

#DONE 正在执行... AFE7950/bringup/S8_ExternalClk_RX_250m_TX_FB_250m_center_care.py 5400MHz

#结束时间2024年02月13日19:50:55.036000

#执行时间= 7.46700000763 s

#==================== 错误:2,警告:1=================== #

---------------- Latte 输出消息结束-------------------------------------------------------

尊敬的 Byungsoo:

只是对脚本不起作用的原因进行一些注释。

如果您愿意、您能告诉我有关所需模式的以下详细信息吗、我将为您创建一个脚本:

此致!

卡米洛

您好,Camilo,

感谢您的答复。

是的、我使用 TSW14J57。

下面我想 介绍设置信息。 外部时钟应为100 MHz。

谢谢你。

尊敬的 Byungsoo:

只是想澄清一些东西。 当您说"External clock 应为 LMK"时、您指的是100 MHz 的输入时钟是否正确? 或者您是指 AFE 的 Fref 输入吗?

如果您参考的是 LMK 的输入、则 LMK 的分配模式将无法与100MHz 配合使用、因为对于 TSW14J57、您的 FPGA 时钟为(通道速率)/40、并且您在下面建议的参数没有可实现这一点的模式。

因此、我为您提供以下选项:

如果您更愿意选择选项2、请告知我。

此致!

卡米洛

您好,Camilo

感谢您的答复。

外部时钟连接到 J14 SMA 连接器。 如您所知、J14 SMA 连接器连接到 LMK04832的 CLKIN1引脚。

正如我所述、我要将 LMK04832分配模式与外部100 MHz 结合使用。

我知道在阅读完您的回复后、Latte 脚本不支持 LMK04832的所有设置。

当我使用外部时钟时、我只能将 FRef 设置为与 lmkParams.inputClk 相同。

我尝试将脚本 fRef 更改为100 MHz。

在本例中、将传递所有。 但是、串行器/解串器通道不会接收来自高速数据转换器专业版的数据。

我附上了脚本。 请检查一下、让我知道哪里出了问题。

谢谢你。

---------------- 脚本的开始-------------------------------------------------------

############################## Read me ####################

#使用外部时钟而不是板载时钟。 而 LMK04832在分配模式下工作。

在 HSDC Pro DAC 选项卡中、选择 AFE79xx_2x2TX_24410;数据速率= 100M

#在 HSDC Pro ADC 选项卡中、选择 AFE79xx_2x2RX_24410;数据速率= 100m -->以采集4个 RX 通道

#在 HSDC Pro ADC 选项卡中、选择 AFE79xx_1x2FB_24410;数据速率= 100m -->以采集2个 FB 通道

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 #使用 HSDC Pro 设置 FPGA (TSW14J56)

############################## 顶级######################

sysParams。 FREF = 100

sysParams。 FadcRx = 2000

sysParams。 FadcFb = 2000

sysParams。 Fdac = 4000

sysParams。 RRFMode = 5 #RRFMode 0:4T4R2F FDD 模式

#RRFMode 1:4T4R1F FDD 模式

#RRFMode 2:4T4R2F FDD 模式四频带

#RRFMode 5:4T4R2F TDD 非共享

#RRFMode 6:4T4R1F TDD 非共享

#RRFMode 7:4T4R2F TDD 共享

#RRFMode 8:4T4R1F TDD 共享

#RRFMode 10:2T2R1F TDD AB / 2T2R1F FDD CD

#RRFMode 11: 2T2R1F FDD AB / 2T2R1F TDD CD

sysParams.externalClockRx=错误

sysParams.externalClockTx=错误

############################## 数字链########################

#### 处方####

sysParams.ddcFactorRx =[20、20、20 ]# RX A、B、C 和 D 的 DDC 抽取因子

sysParams.rxNco0 =[5,400,5400]、#Band0、Band1 (对于 RXA)

[5,400,5400]、#Band0、Band1 (对于 RXB)

[5,400,5400]、#Band0、Band1 (对于 RXC)

[5,400,5400]]# RXD 的 Band0、Band1

#### FB ####

sysParams.ddcFactorFb =[20、20]# FB 1和2的 DDC 抽取因子

sysParams.fbNco0 =[5,400,5400]#Band0 (对于 FB1和 FB2)

#### 发送####

sysParams.ducFactorTx =[40、40、40]# TX A、B、C 和 D 的 dUC 插值因子

sysParams.txNco0 =[5,400,5400]、#Band0、Band1 (对于 TXA)

[5,400,5400]、#Band0、Band1 (对于 TXB)

[5,400,5400]、#Band0、Band1 (对于 TXC)

[5,400,5400]]# TXD 的 Band0、Band1

############################## JESD ########################

#### ADC-JESD ####

sysParams.jesdSystemMode=[1,1]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; Rx -Rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb - fb- fb - fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol=[0,0]# 0 - 8b/10b 编码;2 - 64b/66b 编码

sysParams。 LMFSHdRx =["24410"、"24410"、"24410"、"24410"]

#第2个和第4个值仅对 jesdSystemMode 中的值有效(0,2)。

#对于其他模式,请为第1和第3选择4个转换器模式。

sysParams。 LMFSHdFb =["24410"、"24410"]

sysParams.rxJesdTxScr =[真、真、真、真]

sysParams.fbJesdTxScr =[True、True]

sysParams.rxJesdTxK =[16、16、16、16]

sysParams.fbJesdTxK =[16,16]

sysParams.jesdTxLaneMux =[0、1、2、3、4、5、6、7]#输入您要在每个位置使用的通道。

#例如,如果你想交换每2T 的前两行,

#这应该是[1,,0,2,3],[5,4,6,7]]

#### DAC-JESD ####

sysParams.jesdRxProtocol=[0、0]

sysParams。 LMFSHdTx =["24410"、"24410"、"24410"、"24410"]

sysParams.jesdRxLaneMux =[0、1、2、3、4、5、6、7]#输入您要在每个位置使用的通道。

#例如,如果您要交换每个2R 的前两行

#这应该是[1,,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd =[4、4]

sysParams.jesdRxScr =[真、真、真、真]

sysParams.jesdRxK =[16、16、16]

#### JESD 通用####

sysParams.jesdABLvdsSync= True

sysParams.jesdCDLvdsSync= True

sysParams.syncLoopBack = True #JESD 同步信号已连接到 FPGA

############################## GPIO ##############################

sysParams.gpioMapping ={

'H8':'ADC_SYNC0'、

'H7':'ADC_SYNC1'、

'N8':'ADC_SYNC2'、

'N7':'ADC_SYNC3'、

'h9':'DAC_SYNC0'、

'G9':'DAC_SYNC1'、

'n9':'DAC_SYNC2'、

'P9':'DAC_SYNC3'、

'P14':'GLOBAL_PDN'、

'K14':'FBABTDD'、

'R6':'FBCDTDD'、

'H15':['TXATDD'、'TXBTDD']、

'V5':['TXCTDD'、'TXDTDD']、

'E7':['RXATDD'、'RXBTDD']、

'R15':['RXCTDD'、'RXDTDD']}

############################## LMK 参数####################

lmkParams.pllEn =假

lmkParams.inputClk = 100 #仅当 lmkParams.pllEn = False 时有效

#lmkParams.lmkVcoFreq = 3000;

lmkParams.lmkFrefClk =真

对于 TSW14J56、setupParams.fpgaRefClk = 100 #应等于 LaneRate/40

############################## 记录##########################

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x1 #Modify to 0x1以将寄存器序列保存至日志文件。 执行脚本需要更多时间。

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

#------------------ #

AFE.deviceBringup ()

AFE.TOP.overrideTdd (15、3、15)#位元;4R、2F、4T

---------------- 脚本的结尾-------------------------------------------------------

尊敬的 Byungsoo:

我对您发布的脚本进行了一些更改。 问题是、您只需要一些额外的写入即可将 LMK 设置为旁路模式。

请在 HSDCpro 中使用"AFE79xx_2x2TX_24410"和"AFE79xx_6RX_24410".ini 文件尝试此脚本。

############## Read me ##############

#External clock is used instead of onboard clock. And LMK04832 is working in distribute mode with 100MHz input.

#In HSDC Pro DAC tab, Select AFE79xx_2x2TX_24410; Data Rate = 100M

#In HSDC Pro ADC tab, Select AFE79xx_6RX_24410; Data Rate = 100M ---> To capture 4 RX and 2 FB channels in this order RXA, RXB, FBAB, RXC, RXD, & FBCD

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 # setup FPGA (TSW14J56) using HSDC Pro

############## Top Level ##############

sysParams.FRef = 100

sysParams.FadcRx = 2400

sysParams.FadcFb = 2400

sysParams.Fdac = 7200

sysParams.RRFMode = 5 #RRFMode 0: 4T4R2F FDD Mode

#RRFMode 1: 4T4R1F FDD Mode

#RRFMode 2: 4T4R2F FDD Mode Quad Band

#RRFMode 5: 4T4R2F TDD Non-Shared

#RRFMode 6: 4T4R1F TDD Non-Shared

#RRFMode 7: 4T4R2F TDD Shared

#RRFMode 8: 4T4R1F TDD Shared

#RRFMode 10: 2T2R1F TDD AB / 2T2R1F FDD CD

#RRFMode 11: 2T2R1F FDD AB / 2T2R1F TDD CD

sysParams.externalClockRx=False

sysParams.externalClockTx=False

############## Digital Chain ##############

##### RX #####

sysParams.ddcFactorRx = [24,24,24,24] #DDC decimation factor for RX A, B, C and D

sysParams.rxNco0 = [[5400,5400], #Band0, Band1 for RXA

[5400,5400], #Band0, Band1 for RXB

[5400,5400], #Band0, Band1 for RXC

[5400,5400]] #Band0, Band1 for RXD

##### FB #####

sysParams.ddcFactorFb = [24,24] #DDC decimation factor for FB 1 and 2

sysParams.fbNco0 = [5400,5400] #Band0 for FB1 and FB2

##### TX #####

sysParams.ducFactorTx = [72]*4 #DUC interpolation factor for TX A, B, C and D

sysParams.txNco0 = [[5400,5400], #Band0, Band1 for TXA

[5400,5400], #Band0, Band1 for TXB

[5400,5400], #Band0, Band1 for TXC

[5400,5400]] #Band0, Band1 for TXD

############## JESD ##############

##### ADC-JESD #####

sysParams.jesdSystemMode= [1,1]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; rx -rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb -fb- fb -fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol= [0,0] # 0 - 8b/10b encoding; 2 - 64b/66b encoding

sysParams.LMFSHdRx = ["24410","24410","24410","24410"]

# The 2nd and 4th are valid only for jesdSystemMode values in (0,2).

# For other modes, select 4 converter modes for 1st and 3rd.

sysParams.LMFSHdFb = ["24410","24410"]

sysParams.rxJesdTxScr = [True,True,True,True]

sysParams.fbJesdTxScr = [True,True]

sysParams.rxJesdTxK = [16,16,16,16]

sysParams.fbJesdTxK = [16,16]

sysParams.jesdTxLaneMux = [0,1,2,6,4,5,3,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2T,

# this should be [[1,0,2,3],[5,4,6,7]]

##### DAC-JESD #####

sysParams.jesdRxProtocol= [0,0]

sysParams.LMFSHdTx = ["24410","24410","24410","24410"]

sysParams.jesdRxLaneMux = [0,1,4,5,2,3,6,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2R

# this should be [[1,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd = [4, 4]

sysParams.jesdRxScr = [True,True,True,True]

sysParams.jesdRxK = [16,16,16,16]

##### JESD Common #####

sysParams.jesdABLvdsSync= True

sysParams.jesdCDLvdsSync= True

sysParams.syncLoopBack = True #JESD Sync signal is connected to FPGA

############## GPIO ##############

sysParams.gpioMapping = {

'H8': 'ADC_SYNC0',

'H7': 'ADC_SYNC1',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'DAC_SYNC0',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

############## LMK Params ##############

lmkParams.pllEn = False

lmkParams.inputClk = 100 # Valid only when lmkParams.pllEn = False

#lmkParams.lmkVcoFreq = 3000;

lmkParams.lmkFrefClk = True

setupParams.fpgaRefClk = 100 # Should be equal to LaneRate/40 for TSW14J56

############## Logging ##############

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x1 #Modify to 0x1 to save register scequence to log file. Script takes more time to execute.

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

############## Program LMK ##############

setupParams.skipLmk = False

AFE.initializeConfig()

lmkParams.sysrefFreq = AFE.systemStatus.sysrefFreq

lmkParams.lmkPulseSysrefMode = False

AFE.LMK.lmkConfig()

AFE.initializeConfig()

lmk.head.page.DCLK0_SDCLK1_controls.Analog_Dig_Delay.dclk_mux_lt_1_0_gt_ = 2

lmk.head.page.DCLK12_SDCLK13_controls.Analog_Dig_Delay.dclk_mux_lt_1_0_gt_ = 2

#-------------------------------------------------------------------------------------------------#

## Initiates AFE79xx Bring-up

setupParams.skipLmk = True

## Run init

AFE.deviceBringup()

## RF Enable

AFE.TOP.overrideTdd(15,3,15) # RF Enable Configuration hex(15)=F=0x1111 is all Rx , 1 is single FB=FBab, hex(10)=1010 is only Tx B & Tx D EN3

setupParams.skipLmk = False

由于所使用的 Fref 低于针对片上 PLL 的建议500MHz、因此您在此模式下的相位噪声性能可能不是最佳的。

如果您想使用最大 DAC Fs、我们仍然可以为您提供一个脚本、该脚本将100MHz 外部时钟带到 LMK 以锁定 PLL1、 然后使用板载晶体生成3GHz VCO、为 FPGA 提供参考时钟、以实现能够使用最大采样率的模式。

此致!

卡米洛

您好,Camilo

我测试一下您修改了 Latte 脚本。

下面我附上了 Latte 日志文件。

如果您看到它、您就可以理解。

我使用491.5M 采样率等其他脚本测试板载振荡器。

脚本运行正常、我可以看到 AFE7950射频输出。

---------------- 拿铁日志的统计-------

#====

#正在执行.. 5400MHz_from_TI.py

#开始时间2024年02月20日15:20:34.063000

对于这些速率、不支持1KHz 光栅模式。 更改为32位 NCO 模式。

外部 Sysref 频率应为以下的整数因子:3.125MHz

2T2R1F 编号:0

有效配置:true

laneRateRx:4000.0

laneRateFb:4000.0

laneRateTx:4000.0

2T2R1F 编号:1

有效配置:true

laneRateRx:4000.0

laneRateFb:4000.0

laneRateTx:4000.0

LMK 时钟分频器-器件寄存器复位。

LMK 时钟分频器-器件寄存器复位。

外部 Sysref 频率应为以下的整数因子:3.125MHz

2T2R1F 编号:0

有效配置:true

laneRateRx:4000.0

laneRateFb:4000.0

laneRateTx:4000.0

2T2R1F 编号:1

有效配置:true

laneRateRx:4000.0

laneRateFb:4000.0

laneRateTx:4000.0

外部 Sysref 频率应为以下的整数因子:3.125MHz

2T2R1F 编号:0

有效配置:true

laneRateRx:4000.0

laneRateFb:4000.0

laneRateTx:4000.0

2T2R1F 编号:1

有效配置:true

laneRateRx:4000.0

laneRateFb:4000.0

laneRateTx:4000.0

ChipVersion 的器件初始化:1.3

donot_open_Atharv_full -器件寄存器复位。

芯片类型:0xA

芯片 ID:0x78

芯片版本:0x11

SPIA 可以控制 PLL 页面

释放 PLL Pages SPI 控制。

熔丝组负载自动加载成功完成

无自动加载错误

熔丝组负载自动加载成功完成

无自动加载错误

//固件版本=11000

// PG 版本= 1

//发布日期[dd/mm/yy]= 10/7/19

patchSize=11697

//补丁版本= 165

// PG 版本= 0

//发布日期[dd/mm/yy]= 27/11/21

SPIA 可以控制 PLL 页面

PLL 被锁定

释放 PLL Pages SPI 控制。

SPIA 可以控制 PLL 页面

释放 PLL Pages SPI 控制。

SPIA 可以控制 PLL 页面

释放 PLL Pages SPI 控制。

SPIA 可以控制 PLL 页面

释放 PLL Pages SPI 控制。

Sysref 按预期读取

######################## 设备 DAC JESD-RX 0链路状态#######

通道0:1的 SERDES-FIFO 错误

通道1:1的 SERDES-FIFO 错误

逗号对齐锁定区域0:错误;请检查发送器是否正在发送数据且眼图良好。

逗号对齐锁定区域1:错误;请检查发送器是否正在发送数据且眼图良好。

CS State TX0: 0b00000000。 预计为0b00001010

FS 状态 TX0: 0b00000000。 预计为0b00000101

无法为器件 RX 建立链路:0;警报:0x3000

##################################################

######################## 设备 DAC JESD-RX 1链路状态#######

通道0:1的 SERDES-FIFO 错误

通道1:1的 SERDES-FIFO 错误

逗号对齐锁定区域0:错误;请检查发送器是否正在发送数据且眼图良好。

逗号对齐锁定区域1:错误;请检查发送器是否正在发送数据且眼图良好。

CS State TX0: 0b00000000。 预计为0b00001010

FS 状态 TX0: 0b00000000。 预计为0b00000101

无法为设备 RX 建立链路:1;警报:0x3000

##################################################

#DONE 正在执行... 5400MHz_from_TI.py

#结束时间2024年02月20日15:21:32.608000

#执行时间= 58.5450000763 s

#==================== 错误:10,警告:1============ #

---------------- 拿铁日志结束-------

谢谢你。

尊敬的 Byungsoo:

只是为了澄清一下、脚本最终是否能为您效劳? 我提出问题的原因是、我看到您说"脚本正在工作、我可以看到 AFE7950射频输出"。 但是、您发布的日志显示 JESD 链路没有建立。

如果出现问题、需尝试两点:确保 J57 FPGA 在运行 AFE 启动之前发送 TX 数据、并在启动后运行 AFE.adcDacSync (1)以检查链路状态。

此致!

卡米洛

您好,Camilo

当我看到射频输出时、使用的脚本和测试配置不同。

前面讲过、当我测试不同的脚本时、LMK 时钟源是板载振荡器。

为什么我像这样进行测试、我喜欢检查电路板是否正常工作。 结果表示电路板正在工作。

测试还有另一个含义、测试序列没有问题。

转换器 Pro 等软件在运行 AFE 启动之前发送 TX 数据。

我在 Latte 的 Command Line 窗口中添加了命令 afe.adcDacSync (1)后面的日志。

我在 AFE 启动后发出命令。

谢谢你。

---------------- 日志的开始-------------------------------------------------------

SPIA 可以控制 PLL 页面

释放 PLL Pages SPI 控制。

######################## 设备 DAC JESD-RX 0链路状态#######

通道0:1的 SERDES-FIFO 错误

通道1:1的 SERDES-FIFO 错误

逗号对齐锁定区域0:错误;请检查发送器是否正在发送数据且眼图良好。

逗号对齐锁定区域1:错误;请检查发送器是否正在发送数据且眼图良好。

CS State TX0: 0b00000000。 预计为0b00001010

FS 状态 TX0: 0b00000000。 预计为0b00000101

无法为器件 RX 建立链路:0;警报:0x3000

##################################################

######################## 设备 DAC JESD-RX 1链路状态#######

通道0:1的 SERDES-FIFO 错误

通道1:1的 SERDES-FIFO 错误

逗号对齐锁定区域0:错误;请检查发送器是否正在发送数据且眼图良好。

逗号对齐锁定区域1:错误;请检查发送器是否正在发送数据且眼图良好。

CS State TX0: 0b00000000。 预计为0b00001010

FS 状态 TX0: 0b00000000。 预计为0b00000101

无法为设备 RX 建立链路:1;警报:0x3000

##################################################

#====

---------------- 日志结束-------------------------------------------------------

您好,Camilo

感谢您的答复。

今天、我看到射频输出。 我不知道有什么不同。

现在我选择 AFE79xx_2x2TX_24410。

昨天和之前。 我选择了 AFE79xx_2x2TX_24410-B。 今天我甚至再次选择了 AFE79xx_2x2TX_24410-B。 我可以看到射频输出。

我使用的 Latte 版本是5.4。 TSW14J57上的 LED D2闪烁。

它在工作。

谢谢你。 Calmilo.