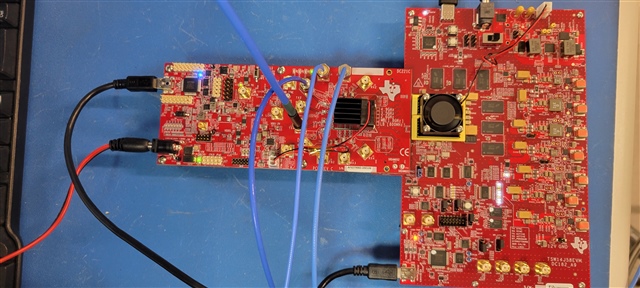

主题中讨论的其他器件:TSW14J58EVM、 AFE7769D

目前我正在设置中挣扎。

在这里、我有几个问题。

Latte 软件是否也可以控制 FPGA 板(TSW14J58EVM)?

当我同时打开 Latte 和 HSDC 时、USB 连接会断开。

看起来 Latte 可以控制 FPGA 板、但如果我只使用 Latte、FPGA 可能无法正确设置。

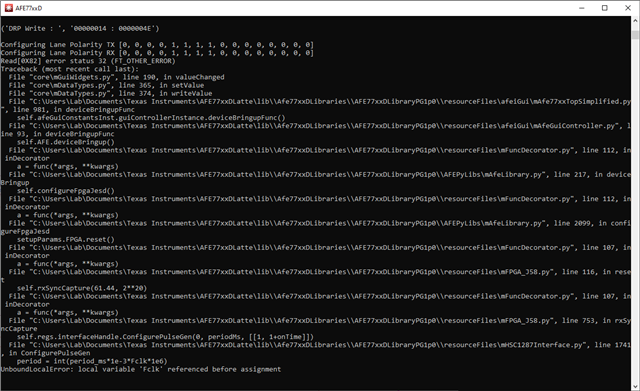

JTAG 和 Vivado 是否必不可少?

我认为 JTAG 是可选的、并且我没有使用 JTAG 连接。 它是否与 Latte 的 FPGA 设置问题有关?

我想先开始测试 TX。

我正在使用 SA 检查 TX 端口并更改设置。

我只能在短时间内看到 LO 泄漏、它消失了。

这意味着 可以正确设置 AFE7769D、我想没有基带信号、它会停止。

文档 sbasag4a、第174页显示了器件可与频率低至122.88Mhz 的 Fref 配合使用。

我认为 AFE7769D 可以接受122.88Mhz 作为参考 CLK、但 Latte 软件配置选项卡不允许我进行设置。

CONFIG 选项卡的下拉菜单仅显示245.76MHz、368.64MHz、491.52Mhz

我认为"CONFIG"选项卡应该包括下拉菜单中的122.88MHz。

启动 HSDC 时、我看到"固件版本和 dll 版本不匹配"消息。

如何解决该问题?

提前感谢您的帮助。