您好

我使用了 ADC12DJ5200RF EVM GUI。 不会与 FPGA EVM 连接。

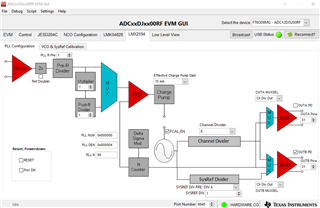

根据 PIC1 JMODE 1设置,jesd204C 的块 SERDES PLL 锁定指示灯亮起。

但 PIC2 JMODE 2 SERDES PLL 锁定不亮。

不同之处是什么?

SERDES PLL 锁定的含义是什么?

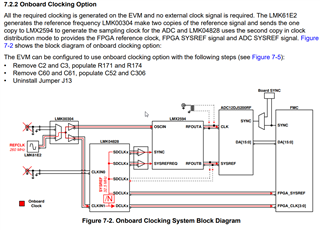

图1:

图2:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

我使用了 ADC12DJ5200RF EVM GUI。 不会与 FPGA EVM 连接。

根据 PIC1 JMODE 1设置,jesd204C 的块 SERDES PLL 锁定指示灯亮起。

但 PIC2 JMODE 2 SERDES PLL 锁定不亮。

不同之处是什么?

SERDES PLL 锁定的含义是什么?

图1:

图2:

您好!

SERDES PLL LOCK 位意味着串行器 PLL 已锁定、串行器 PLL 用于设置 SERDES 速率频率。

我可以看到您正在对 EVM 使用板载时钟模式,您能否确认您已进行了 EVM 用户指南第20页所列的所有必要硬件更改 。

如果是、您可以使用示波器验证来自 LMK04828的 FPGA 参考频率是否与 EVM GUI 中的调用频率相匹配。

此致!

埃里克

您好!

您能否首先确认您进行了以下硬件更改、特别是...

这些更改是进行板载时钟工作所必需的。 您还可以查看下面的方框图。

除非您使用非常高的示波器、否则您将无法看到 LMX2594的 RFOUTA、您应该能够看到 LMX2594的 RFOUTB 信号、但该信号也可能具有很高的频率、具体取决于您使用的示波器类型。

我不知道你在图2中想做什么,但我不建议它。 如果按照我上面建议的更改进行操作、您将更容易实现 ADC 与板载时钟一同运行。

我也不知道图3是在试图显示什么,你能详细说明吗?

我不建议将 FPGA_CLKA_FMC_P 和 SYSREF_ADC_LMK_P 用作 ADC 输入信号。

谢谢。

埃里克

您好!

请参阅我之前关于测量 LMX 输出的意见、

除非您使用非常高的示波器、否则您将无法看到 LMX2594的 RFOUTA、您应该能够看到 LMX2594的 RFOUTB 信号、但该信号也可能具有很高的频率、具体取决于您使用的示波器类型。

RFOUTA 是您向 ADC 提供的采样频率、它将是1000MHz、这基于您在共享的 GUI PIC 中进行的编程。

如果希望尝试探测时钟信号、请尝试使用 LMK04828提供的时钟信号、频率会低得多、应该能够探测时钟信号。 您如何进行这些测量、您是否在使用示波器? 如果是、那么示波器的带宽是多少。

您是否还能够采集并显示数据 ?

此致!

埃里克

Eric、您好:

我使用了板载时钟选项。

我按照 adc12dj5200RFEVM 的说明操作:

->移除 C2和 C3,填充 R171和 R174

->移除 C60和 C61,安装 C52和 C306

->卸载跳线 J13

我设置 EVM GUI 用户输入: JMODE2 , FS selection : 1000Msps.

我使用的示波器模型是 RTM3044。 我能够看到信号 FPGA_CLKB_FMC_P (100MHz)和 FPGA_SYSREF_FMC_P (3.125MHz)(来自 LMK04828)。

按照数据表第19页(板载时钟选项)板载时钟系统方框图 LMK04828输出到 LMX25's 的输入(SYNC , SYSREFREQ : 3.125MHz ),但我看不到 LMX25INGS 的 RFOUTA 和 RFOUTB。

LMX25200 RFOUTA 和 RFOUTB 输入的信号。 并且这两个信号的值必须与 FPGA 的 FPGA_SYSREF 和 FPGA_CLK 相同。

因此我无法看到串行器/解串器 PLL 锁定灯处于开启状态。 但我更改 JMODE1、SERDES PLL 锁定灯将点亮。

我不知道有什么不同?

您好!

您能够正确测量 FPGA_CLK 和 FPGA_SYSREF 这一事实意味着正在正确设置 LMK04828。

正如我在先前的消息中所说的 、除非您具有超高带宽示波器(RTM3044并非仅是具有带宽的100MHz、您将无法看到信号) LMX2594的 RFOUTA 设置为 ADC 采样时钟1GHz、 根据示波器、您将没有足够的带宽来测量此信号 。 LMX2594的 RFOUTB 通道默认断电、因为该输出仅用于参考频率、而这是不需要的。

您可能会探测到 LMX2594的 OSCIN 来自 LMK00304、这应该是此芯片的100MHz CLKOUTA 将进入 LMX、CLKOUTB 将进入 LMK04828。 它们都应该是100MHz。

LMX 将获取该参考信号、并使用 PLL 将其乘以正确的采样频率、在使用 GUI 对 ADC EVM 进行编程后、检查 GUI 的 LMX2594选项卡、确保它看起来像这样。

我们可以通过执行以下 OSCIN = 100MHz、PLL N = 80、通道分频器= 8来计算通道 A 的输出

OSCIN*PLL_N/CHANNEL_DIVIDER = 100 MHz * 80/8= 1000MHz = 1GHz。

SERDES PLL 锁定未打开会带来问题、这意味着器件可能没有获得正确的采样时钟频率、我会再次检查我向您展示的这些设置、并确保它们都正确无误。

此致!

埃里克

您好!

ADC 在默认情况下不需要 sysref 便可运行、因此您可以将其保持关闭状态以进行运行。 如果您想要将其打开、您可以像您已经完成的那样将其启用、要更改频率、您可以增加在 RFOUTB 的路径上看到的分频器。 缺省情况下它的设置方式是 OSCIN*PLL_N/SYSREF_DIV_PRE/SYSREF_DIV 给我们100MHz *80/4/1= 2000 MHz。 如果您想降低该频率、增大 SYSREF_DIV 下拉电阻、例如、您可以将其设置为64、并且您应该会看到31.25 MHz 的输出。 您还可以使用"OUTB Pow"下拉菜单来增加信号强度。

您是否能够验证 LMX2594的 OSCIN 信号?

谢谢!

埃里克

我所做的不是调整 LMK 分频器、您可以将它们保持在1、这实际上意味着您将绕过您在 LMK04828的 CLCKIN_1引脚上输入的信号。 然后、您可以根据提供的屏幕截图、将 LMK61E2编程为您所需的参考频率、在案例200 MHz 中它看起来是什么样的。 您必须注意的一点是、在您更改 LMK61E2的频率输出后、您还必须调整 LMX2594上的分频器设置、以便仍为 ADC 提供正确的采样频率。 下图显示了所有时钟的工作原理。 在板载时钟模式下、LMK61E2为 LMK04828 (用于生成 FPGA 时钟信号)和 LMX2594 (用于生成 ADC 采样时钟)提供基准

此致!

埃里克

您好!

1) 1)是的、SERDES 速率与线速率相同。

2)需要发送到 FPGA、即面向侧的 JESD IP 应用的 FPGA 参考时钟、以及 SYSREF 相关的计时。这有基于 JESD PHY 宽度的严格要求、即32位64位128位。 另一个时钟是 FPGA 中 PHY 的 GBTCLK、用于生成 JESD 链路所需的线速率频率、该时钟的限制较小。

FPGA 参考时钟的具体要求取决于编码类型...

在8b10b 模式下

FPGA 参考时钟=线速率/80、如果 PHY 设置为将每个通道反序列化为64位、则满足此要求

FPGA ref clock = Linerate/40、如果 PHY 设置为将每个通道反序列化为 32位、则会出现这种情况

在64b66b 模式下

FPGA 参考时钟=线路速率/66、 如果 PHY 设置为将每个通道反序列化为64位、则满足此要求

FPGA 参考时钟=线路速率/33、如果 PHY 设置为将每个通道反序列化为 32 位、则满足此要求

FPGA 参考时钟=线路 速率/132、如果 PHY 设置为将每个通道反序列化为128位、则这对于16Gbps 以上的线路速率也是必需的

通常、对于8b10b 模式、我们只关注线速率/80;对于64b66b 模式、我们只关注线速率/66、因为我们的 PHY 的宽度为64位。 但是、您可以根据需要进行更改、以满足时钟要求。 这些 FPGA 参考时钟可乘 以任何整数、以满足您的要求 、并且应仍然正常工作。 对于 GBTCLK、主要要求 是将其保持在 FPGA VCO 范围内、以生成所需的链路速率时钟。 通常、我们将其设置为与 FPGA 基准时钟频率相匹配。

因此、在本例中、您可以展示上面的公式来计算 SERDES 速率、而 FPGA 参考时钟速率

FS = 2000MSPS

SERDES 速率= FS*r 在本例中 r = 3.3、该值可在第96页的操作模式表中找到、仅此 JMODE

因此 SERDES 速率= 6600 MSPS

FPGA 参考时钟等于 SERDES 速率66乘以

FPGA 参考时钟= SERDES/66 = 6600/66 = 100 MHz

希望这对您有所帮助。

埃里克