请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

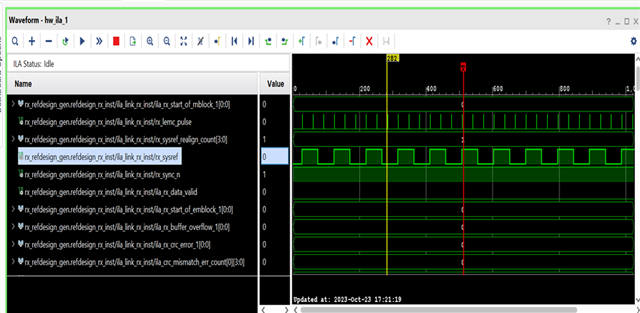

器件型号:AFE7950 我在将 zcu102_64b66b 参考设计从8通道设计移植到2通道设计时遇到了问题。 用于评估 EVM7950上的 AFE7950的具有8个 JESD 通道的 TI xzcu102 64/66位参考设计在提供8个通道时能够可靠地 运行、但在重新配置为通过2个通道运行时由于移植更改而无法正常工作。 TX 侧、即 DAC 侧正在发送音调、但 RX 侧始终未演示 FPGA 中的有效数据处于活动状态 、以指示 FPGA 收发器正在锁定到来自 AFE7950的有效 JESD 流。 以下是使用与该设计集成的 Vivado 硬件调试工具捕获的 RX 端行为。 我还包含了一个文档、详细说明了我根据参考设计随附的说明确定的必要更改。 如果能提供任何帮助,说明为什么它不起作用,我将不胜感激。 谢谢