Other Parts Discussed in Thread: AFE8030

主题中讨论的其他器件:AFE8030

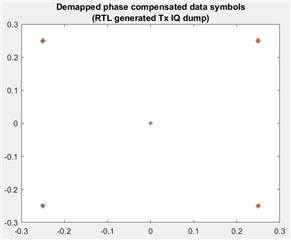

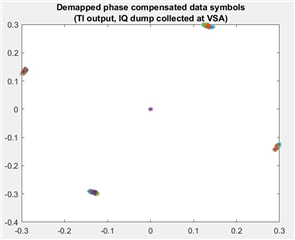

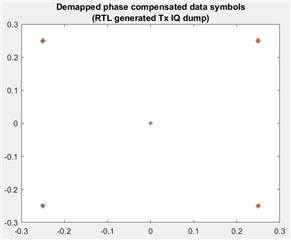

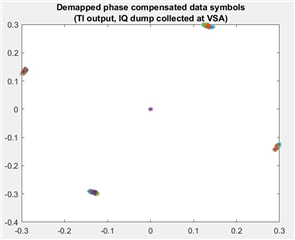

在 RTL 中生成的 Iq ----------------------------------------------------- JESD 接口------------------------------------------------------- > TI DAC (4.4GHz)-> VSA (4.4GHz)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: AFE8030

Shiva、您好!

只要 Fref (参考频率)以及 AFE80xx 片上 PLL 处于稳定状态并保持锁定状态、AFE80xx 的 TX 部分将以固定频率保持稳定。 当 AFE80xx 的 TX 输出相对于 Matlab 脚本的观察路径旋转时、QPSK 会进行旋转。

到 TX 输出的 Matlab 和观测路径是 QPSK 解调中的频率偏移补偿源。 如果初始频率偏移估算与5G NR 帧结束时的最终偏移估算不同、则会发生相位旋转。

请告知 AFE8030 EVM 是否通过通用参考锁相到观察路径/仪器。 这是测试设置侧的一个关键点。

就 AFE80xx 本身而言、您需要检查参考频率和片上 PLL 是否已锁定且稳定。 如果 AFE80xx 本身在时钟级别上正常工作、它所处的级别将低于在5G NR 级别进行的频率偏移补偿。