Other Parts Discussed in Thread: AFE7769DEVM, AFE7769D, AFE7769

主题中讨论的其他器件: AFE7769D、 AFE7769

您好、TI 团队、

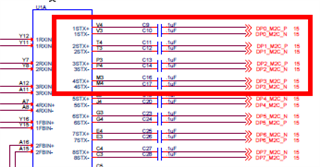

我看到 AFE7769DEVM 上的串行器/解串器通道交换、CPLD 在 AFE7769D 器件中设置了交换的通道吗?

假设、如果我要设计一个与 AFE7769DEVM 匹配的 FPGA FMC 连接器、我只想再次确认我不需要在我身边交换串行器/解串器通道、是这样吗?

谢谢。

此致、

阿尔德