您好

我们正在将 AFE7900EVM ADC 用作发送器、将 Stratix10评估板用作我们项目的接收器。

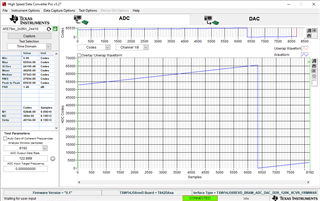

最新版本的 AFE79xx GUI 用于参数设置和 AFE7900EVM 器件启动。

参数和输入规格:

通道速率:4915.2 MHz

FS:2949.12 MHz

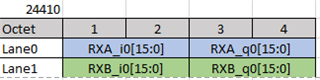

LMFSHd :"12410"与2通道模式

DDC 抽取率:24

出于测试目的、使用 GUI 发送斜坡测试模式、并使用 Quartus Prime 20.2软件从 JESD IP 内核捕获64位输出数据。

用于从捕获的数据中查看斜坡模式的数据格式是什么?

若要从信号发生器发送 IF / RF 数据、需要对 GUI 设置进行哪些更改?

此致

Soumya