主题中讨论的其他器件: LMK04828、

您好!

我正在使用两个 AFE7950器件开发毫米波应用。

我的板包含 MPSoC (XCZU11EG@AMD)+ LMK04828 + AFE7950 (x2)配置。

AFE7950器件是否适用于我的毫米波应用、包括波束形成?

2. AFE7950中是否有允许在内部通道之间校准 NCO 相位的功能?

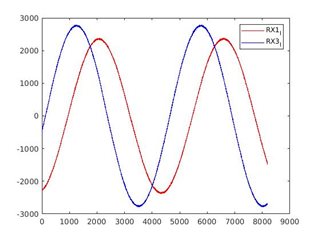

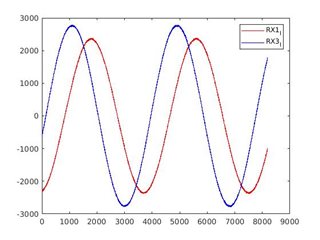

TX/RX 通道之间似乎存在相位差。

在加电/断电时、相位差保持恒定(例如、Ch2-Ch1:55°)。

这可能是由于 AFE7950中的内部 NCO 相位差所致。

AFE7950中是否有允许内部通道之间 NCO 相位对齐的功能?

或者、我是否应该使用 NCOx_PHASE_OFFSET 寄存器来纠正此问题?

谢谢!

此致、

帕克。