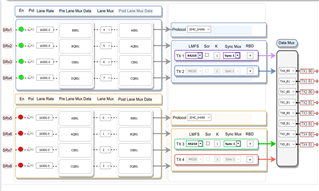

我们有一个连接到 TI AFE7950的 AMD Versal 定制设计。 Versal 包含一个 AMD JESD204C 发射内核、我们将从 LUT 发送 IQ 正弦/余弦数据。 问题是在 AFE 配置过程中、出现任何错误的可能性只有50/50、但另外一半的时间我看到多个警报和错误似乎始终与不良的 RBD 值相关。

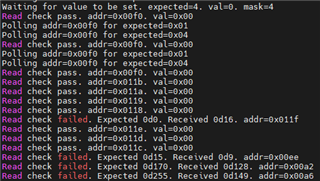

从 Latte 生成的 RBD 值(如下所示)为4。 我从读取通道计数器运行了 TI SBAA543中记录的计算、其中所有读回的值均为0: RBD =(0 + 4)%(64 * 1)= 4% 64 = 4

计算出的 RBD 值似乎与 Latte 中的值匹配、但间歇性链路初始化失败似乎表示 RBD 值错误。 我很好奇您是否对如何进行进一步调试/调查有任何建议。

我们已使用 AMD 的 IBERT 工具以16.5 Gbps 的速率在 FPGA 和 AFE 之间完成了 PRBS31链路测试、但未检测到任何错误。 被俘的眼睛看起来也很好。

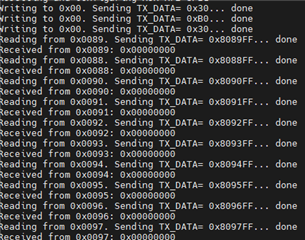

我的另一个问题是、您是否可以使用 SPI 命令来运行 cafe adcDacSync 命令? 我看到这里被引用了、但我们无法直接连接到 AFE 和 PC、因此我们将通过 FPGA 发送 SPI 命令。