工具与软件:

您好!

我们希望确认 DAC38RF82的潜在配置适用于我们的应用。

我们希望从 FPGA 输出两个 I/Q 流、并且需要避免射频频率重叠。

假设我们有两个带宽为100MHz 的 I/Q 流、我们需要在输出端相应地(例如并排)对其进行空格。

参数:

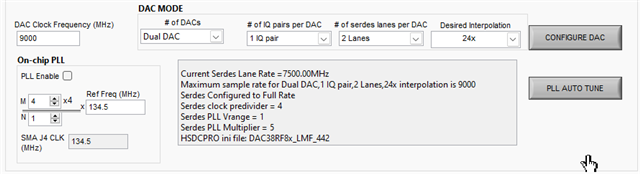

- DAC 时钟频率:3300 MHz

- DAC 模式:单路 DAC A

- IQ 对:2

- JESD204通道:4

- 插值:24倍

- 串行器/解串器速率:2750MHz

射频输出:

- Output1:1900 MHz [带宽:1850-1950]

- output2:2100 MHz [带宽:2050-2150]

以下设置是否可以正常工作?

我还担心3300MHz DAC 时钟过于接近2GHz 中心频率。 这是个问题吗(按奈奎斯特项或失真)?

我无法使用6600 MHz、因为 SERDES 通道速率达到5500 MHz、这高于 DAC 限制?

提前感谢、

Ilias