工具/软件:

TI 团队大家好、

我对硬件触发模式有疑问。

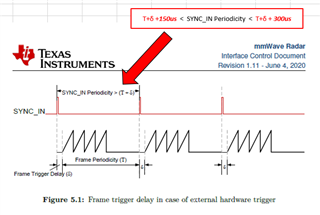

文档"毫米波雷达接口控制文档版本1.11"指出脉冲的周期配置为在前一帧完成后150us 出现、建议前一帧结束和硬件脉冲上升沿之间的时间差小于300us。

我认为、如果图表中显示了上述内容、则会如下图所示(T+δ+150us < SYNC_IN PERIODICITY < T+ADC δ+ 300us)

我的理解是否正确?

此致、

Kei

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

TI 团队大家好、

我对硬件触发模式有疑问。

文档"毫米波雷达接口控制文档版本1.11"指出脉冲的周期配置为在前一帧完成后150us 出现、建议前一帧结束和硬件脉冲上升沿之间的时间差小于300us。

我认为、如果图表中显示了上述内容、则会如下图所示(T+δ+150us < SYNC_IN PERIODICITY < T+ADC δ+ 300us)

我的理解是否正确?

此致、

Kei

您好、Santosh、

感谢您的答复。

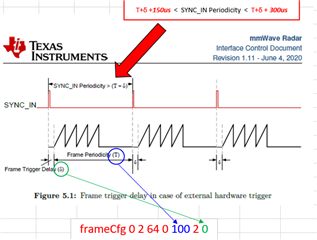

我认为帧触发延迟(在下图中由 δ 表示)由 frameCfg 的第7个参数设置、帧周期(在图中由 T 表示)由第5个参数设置。

这是正确的吗?

此外、如果 δ 需要 T+FET +150us < SYNC_IN PERIODICITY < T+FET δ+ 300us 且 SYNC_IN 脉冲周期是固定的(例如100ms)、则需要将帧时间配置为99.70 ~ 99.85 (帧触发延迟为0)之间。

我的理解是否正确?

此致、

Kei

你好、Kei。

我认为帧触发延迟(在下图中用 δ 表示)由 frameCfg 的第7个参数设置、帧周期(在图中用 T 表示)由第5个参数设置。

这是正确的吗?

您是对的。

此外、如果 δ 需要 T+FET +150us < SYNC_IN PERIODICITY < T+FET δ+ 300us 且 SYNC_IN 脉冲周期固定(例如100ms)、则我需要将帧时间配置为99.70 ~ 99.85 (帧触发延迟为0)。

我的理解是否正确?

我认为这是正确的,虽然我不知道这些数字是否包括这些边界。

此致、

Santosh