主题:AWR2544中讨论的其他器件

工具/软件:

您好、

我正在 awr2544上开发 CSI2驱动器、以支持通过 CSI2-TX 流式传输原始 ADC 数据。 另一方面、我将使用 TMDS273x 的 CSI2-RX 接收该原始 ADC 数据、并在 AM273x SoC (FFT、CFAR...)上进行进一步处理。 它基于 Cbuff LVDS 模块实现。

不过、 一些 CSI2寄存器上的打包配置不会令人感到困惑。 以下是 CSI2寄存器可能需要您帮助:

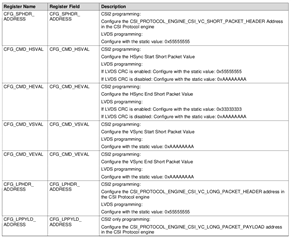

- CFG_SPHDR_ADDRESS - 在 CSI 协议引擎中配置 CSI_PROTOCOL_ENGINE_CSI_VC_SHORT_PACKET_HEADER 地址

- CFG_LPHDR_ADDRESS - 在 CSI 协议引擎中配置 CSI_PROTOCOL_ENGINE_CSI_VC_LONG_PACKET_HEADER 地址

- CFG_LPPYLD_ADDRESS - 在 CSI 协议引擎中配置 CSI_PROTOCOL_ENGINE_CSI_VC_LONG_PACKET_PAYLONG 地址

- CFG_CMD_HSVAL - 配置 HSync Start Short Packet 值

- CFG_CMD_HEVAL - 配置 HSync End Short Packet 值

- CFG_CMD_VSVAL - 配置 VSync 开始短数据包值

- CFG_CMD_VEVAL - 配置 VSync End Short Packet 值

我提到了 MIPI CSI2 v1.3规范、但是我找不到有关该值的太多信息应写入上述寄存器。

您能否建议这些寄存器的值、以便使 awr2544上的 CSI2-TX 引擎和 AM273x SoC 上的 CSI2-RX 引擎正常工作?

谢谢!

QHLam