请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMAG5170-Q1主题: TMAG5170 中讨论的其他器件

工具/软件:

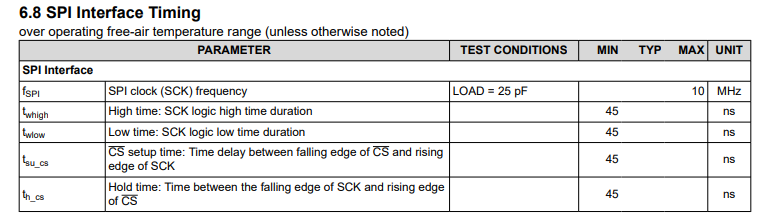

大家好、我正在研究是否可以在具有来自 LTC6820 的 SPI 接口、在时钟频率高达 1MHz 的应用中使用 TMAG5170-Q1。 长话短说、TMAG5170-Q1 的时钟信号输入占空比无法保证为 50%、甚至在 40-60%的范围内。

因此、我的问题是:除了此器件数据表中规定的接口时序要求外、是否有任何占空比要求?

此致、

b.