主题中讨论的其他器件: SN74LVC3G17、 SN74LVC1G74、 ADS1248、 TDC1000

我遇到了一个奇怪的问题:

-我开始测量(config1=c3h、所有其他寄存器的默认值、时钟为16MHz)

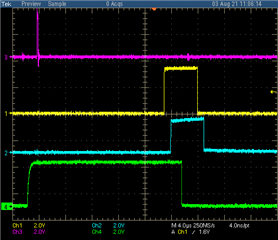

为此,Trigg 从低电平转换为高电平

- 500ns 后、INTB 从低电平转换为开路(如果尚未打开)

- 3000ns 后、开始从低电平到高电平的转换(并在测量的剩余时间内保持高电平)

为此、Trigg 会立即从高电平转换为低电平(即 TDC7200确实会看到开始边沿)

- 10000ns 后、停止从低电平到高电平的转换(并保持高电平)

-在5种情况中,大约有4种情况下,测量成功终止(INTB 变为低电平)

-在大约5种情况中的1种情况下、不会发生任何情况:INTB 保持打开、寄存器表示 TDC7200仍在测量、没有溢出。

由于没有发生溢出、我认为 TDC7200错过了启动边沿、尽管它使 Trigg 变为低电平。 也就是说、TDC7200都能看到并忽略起始边沿。

有什么想法、有什么问题吗? TRIG 和 START 之间的时间是否有最大值(数据表仅列出标称值、无最大值)? 是否存在起始脉冲持续时间的最大值(数据表仅列出最小值)? 是否必须将 START 置为低电平才能检测到 STOP?