您好!

我们有一个具有两个 AFE5818的 PCB、这两个器件具有相同的电气原理图配置并共享相同的电源。

其中一个不响应我们的 SPI 通信。

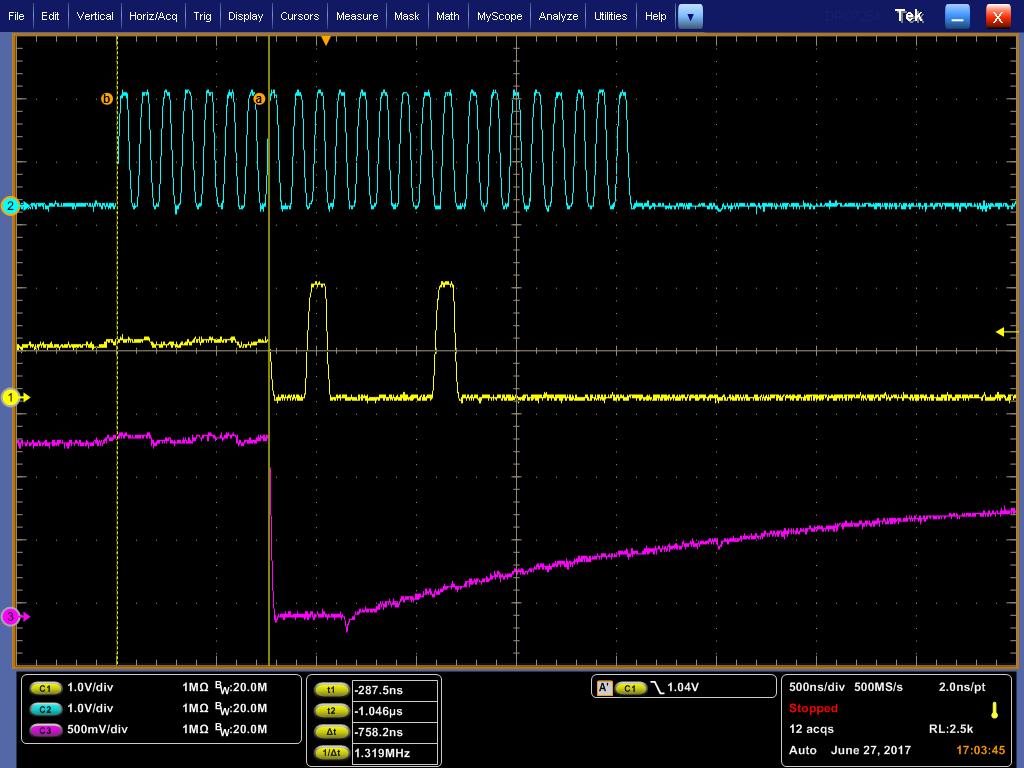

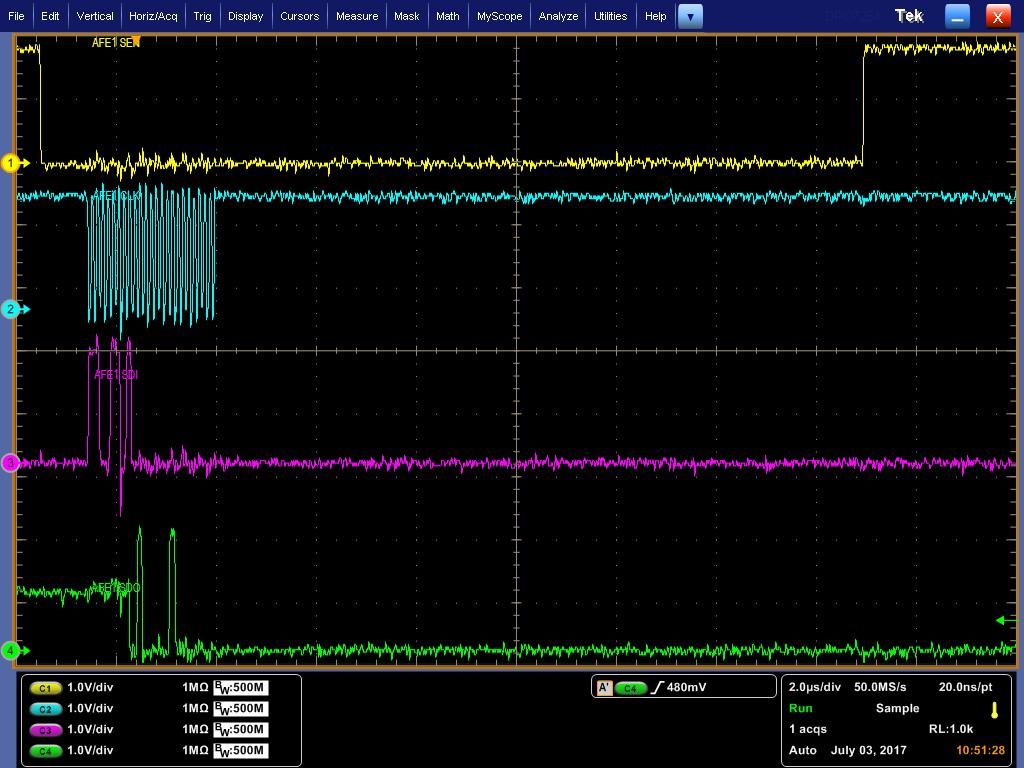

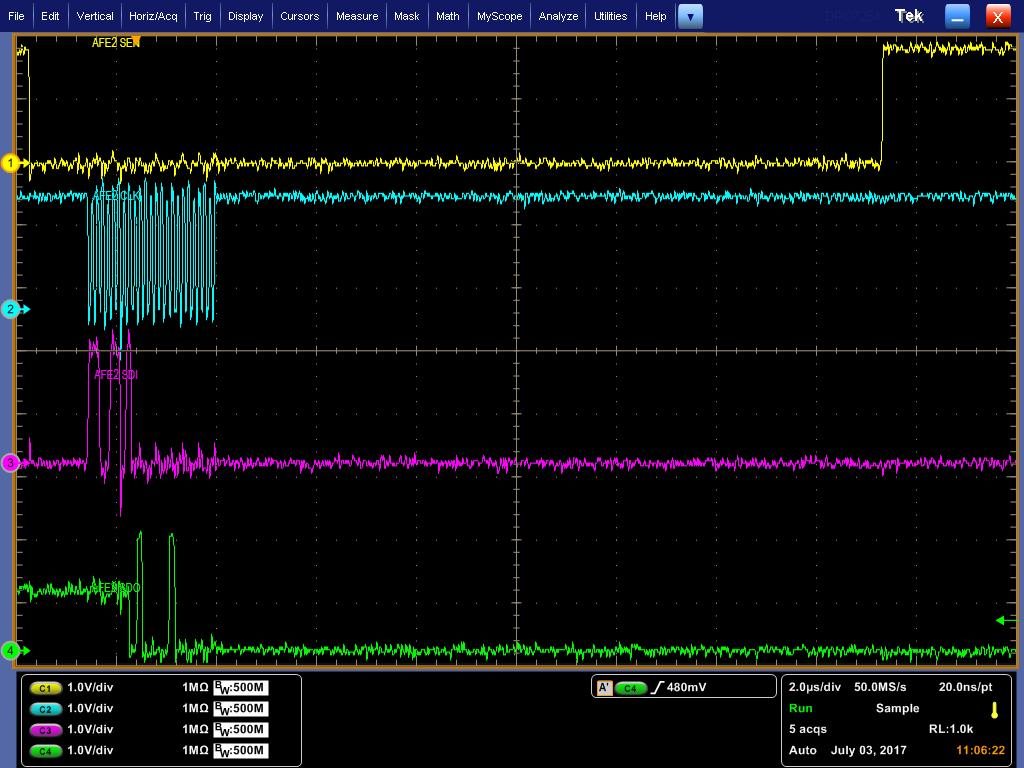

-两个 AFE 上的所有 SPI 信号都相同

-I/O 配置正确

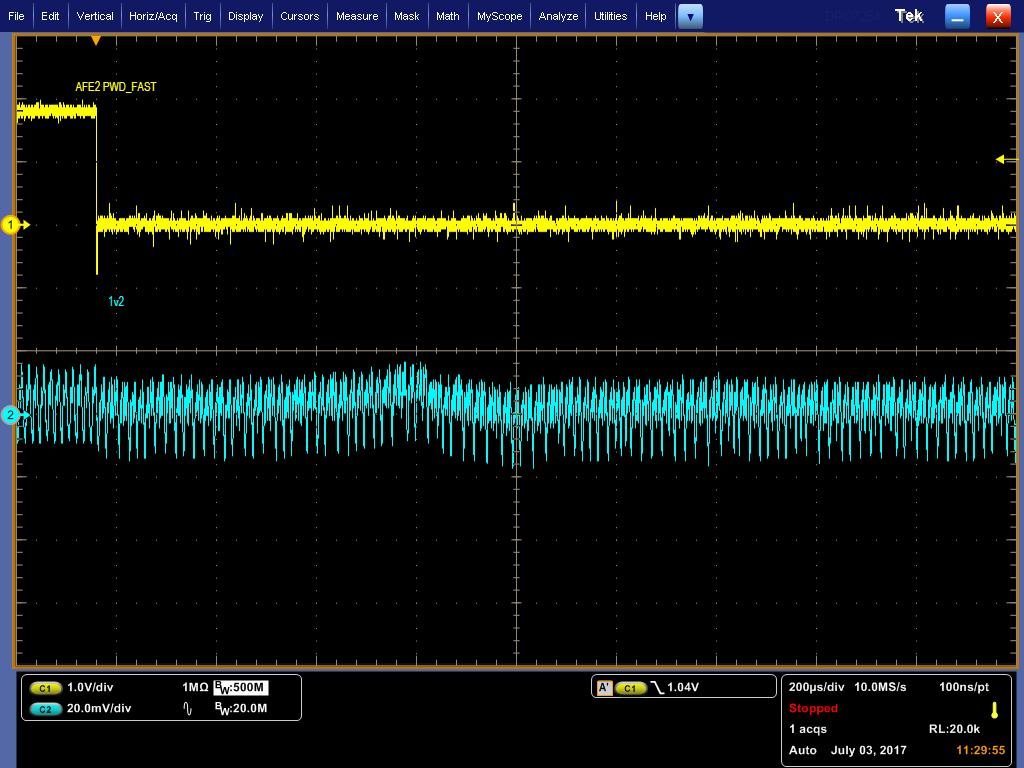

-所有电源轨上的电源纹波< 20mV

-配置和断电引脚释放后、未在所有电源轨上检测到电源压降。

-时钟在两个 AFE 上的行为似乎相同

-我们尝试将所有 AFE2信号连接到 AFE1信号 (其 SDO 除外)

-上电时的 AFE1 SDO 测量值约为0.3V、而不良的 AFE2 SDO 为1.8V

我希望您能帮助解决这个问题、甚至能告诉您如何使第二个 AFE 按其所做的方式运行(在第一个 AFE 执行时停止运行、 并立即释放线路)

此致、

Rotem

编辑:根据客户要求删除设计文件。