请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMP112 您好、专家、

我们有一个与用于确认位的 TMP112 I2C 通信相关的问题。

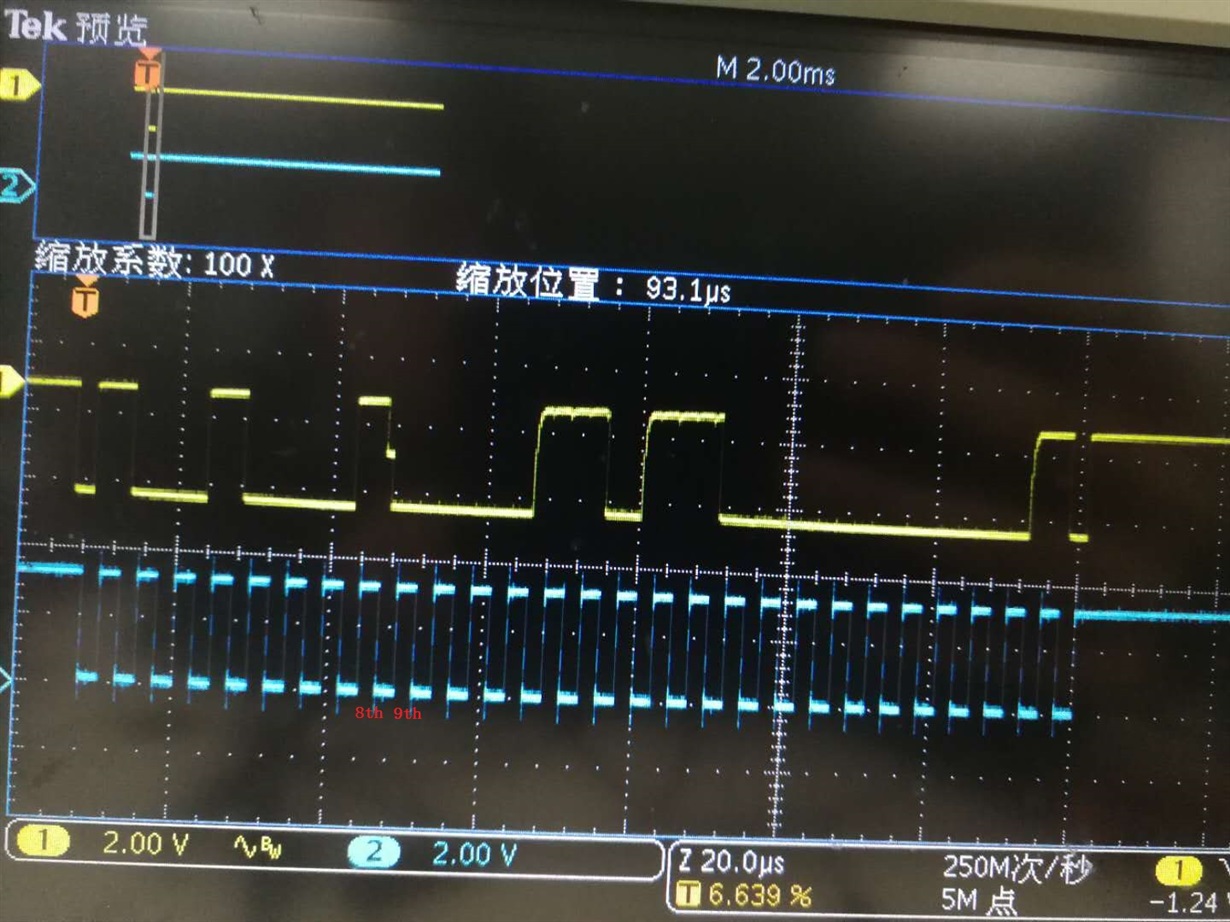

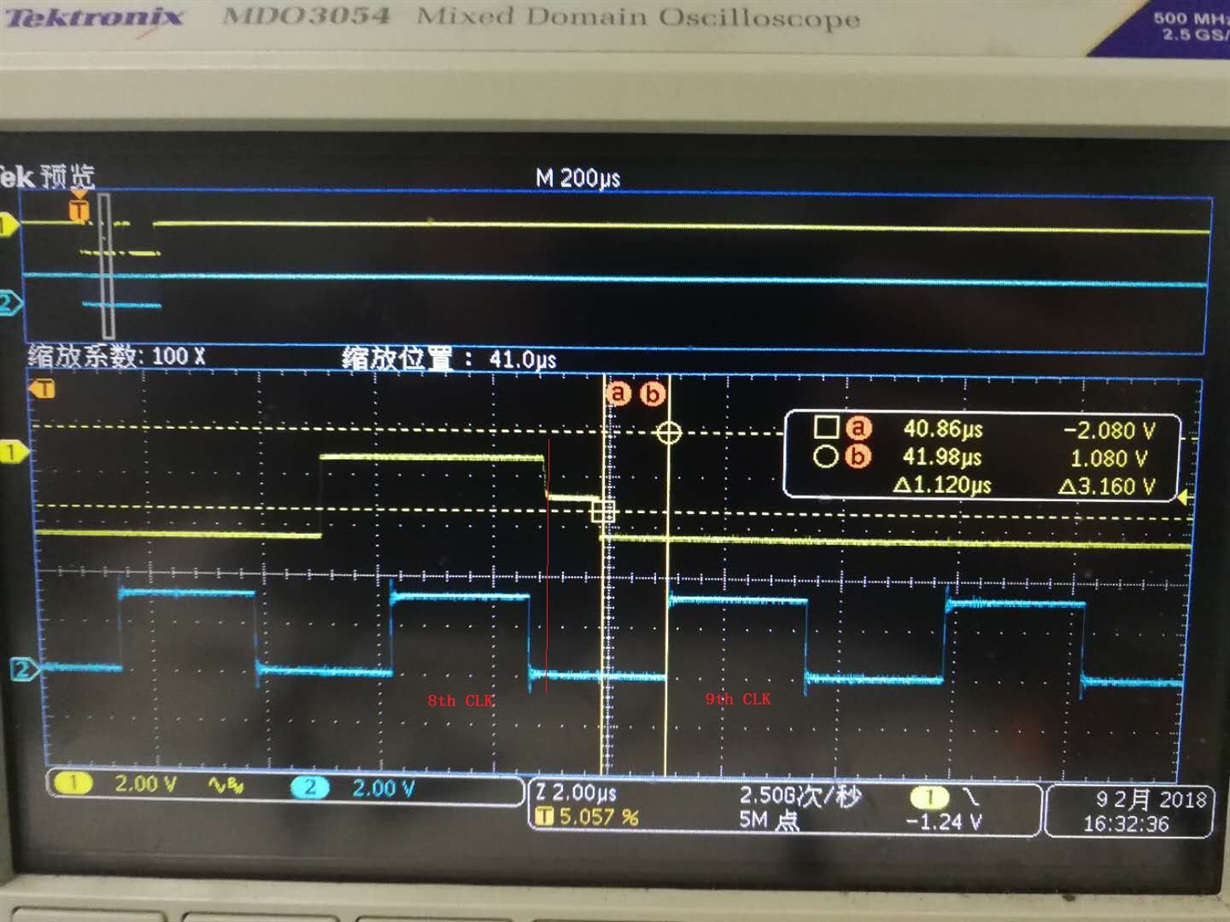

有关 I2C 通信、请参阅以下捕获。 我们的观察结果表明、TMP112将在第8个 SCL 时钟的下降沿将 SDA 驱动为低电平以进行确认。 在第8个 SCL 时钟处、因为我们没有从主器件侧释放 SDA、这会导致中量程电压。

TMP112是否被设计用于在第8个 SCL 时钟的下降边沿上提供确认?

谢谢

周