器件型号:TDC1000-TDC7200EVM

大家好、团队成员

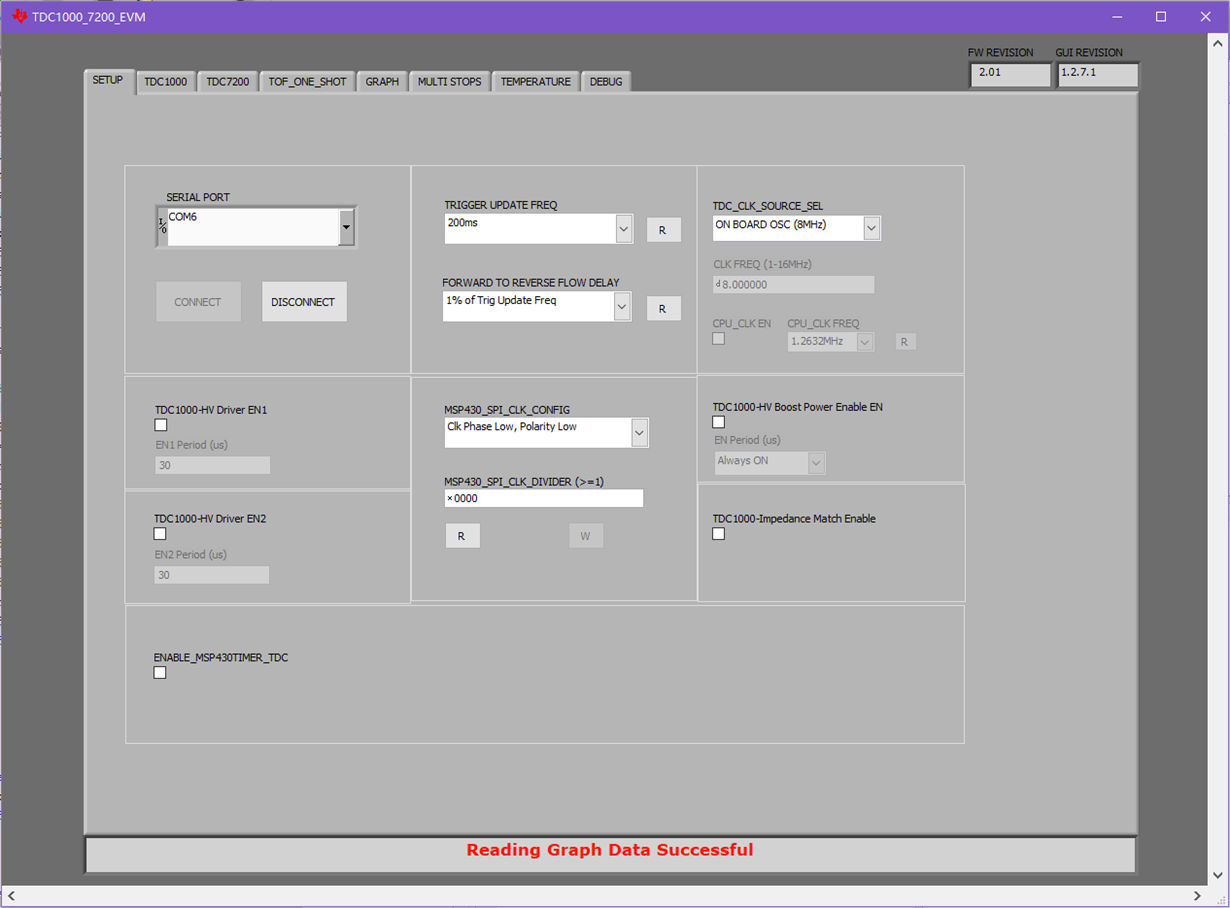

我上周购买了 TDC1000-TDC7200EVM、它在零流量测试中表现出了出色的性能。

我还在几个月前设计了一个基于 TDC 的电路板、它使用 TDC-GP21作为停止表、使用 TDC1000作为 AFE。 但测试结果甚至比我们早期采用单独模拟电路的设计更差,正如我的同事在中所描述  的那样。

的那样。

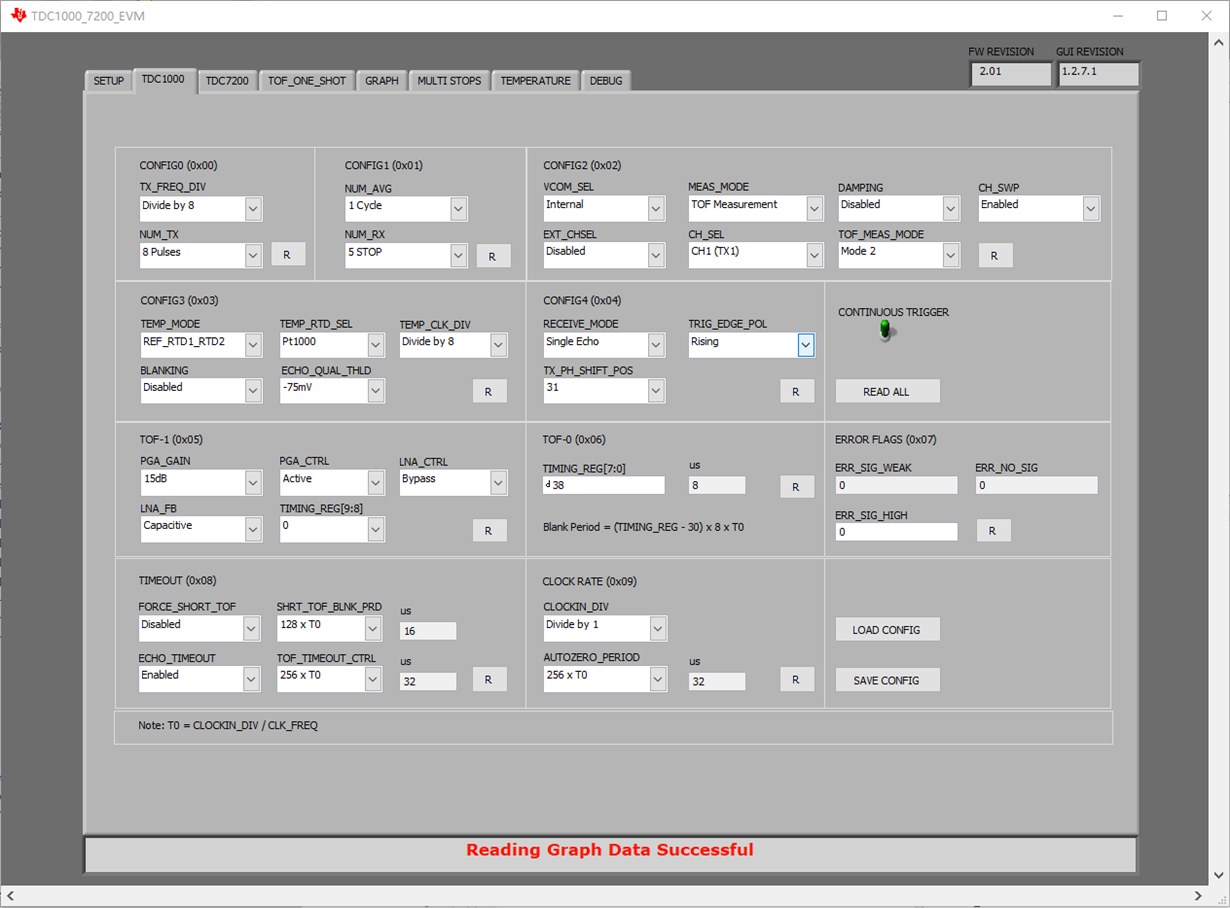

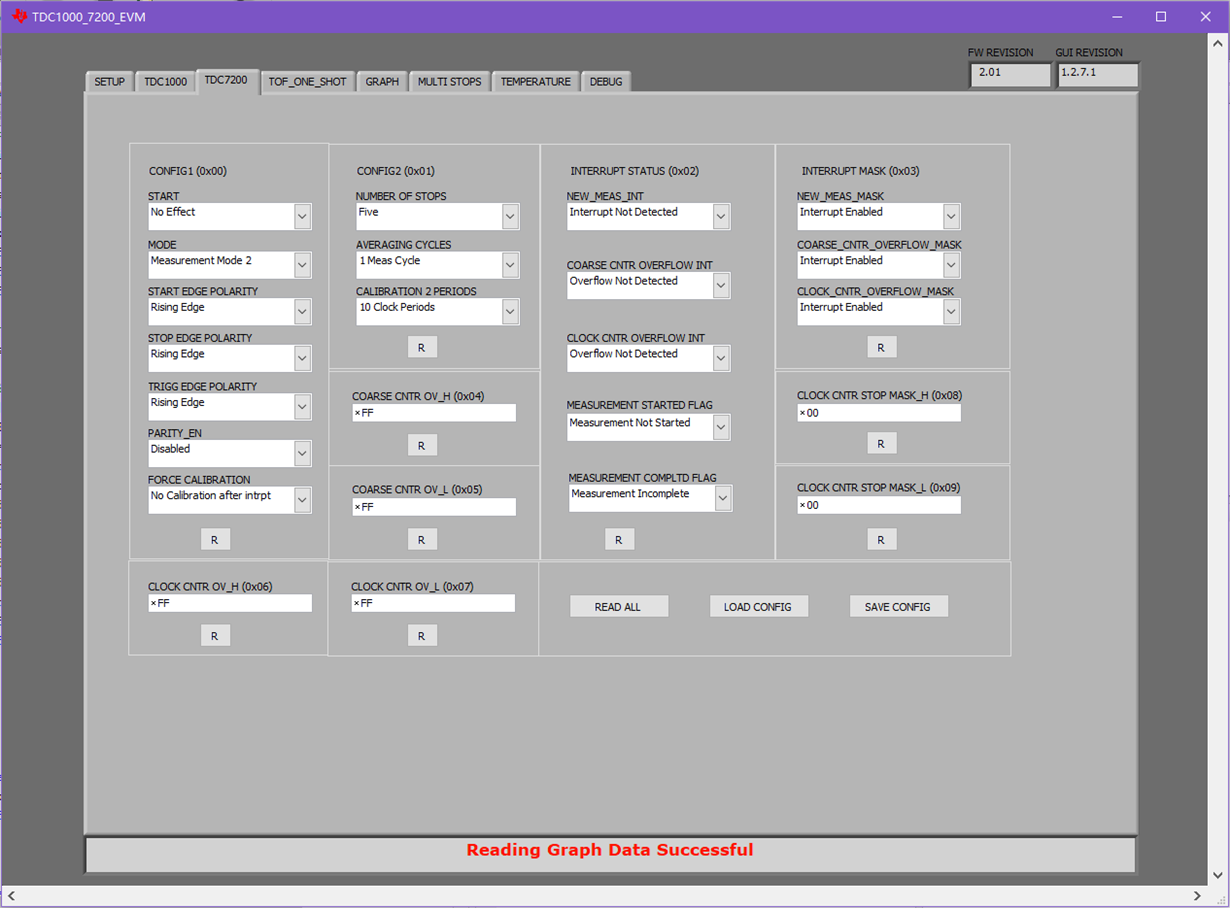

附件中显示了我使用 TDC1000进行的设计。 与 EVM 的主要区别在于秒表、而 TD-GP21的分辨率也高达50ps。 因此、我认为这不会导致该大误差。 我总结了一些可能的问题,如下所示:

TDC-GP21具有一个外部4MHz 门槛、而 TDC1000使用 MCU 的4MHz 时钟;

2. TDC1000由两个3%的线性稳压器(3V 和5V)供电;

可能是 PCB 布局问题?

问题1 我已经进行了各种测试、但仍然没有发现任何问题。 我想知道您是否可以通过设计发现任何重要问题或有任何推荐的解决方案。

e2e.ti.com/.../TDC-based-design.pdf

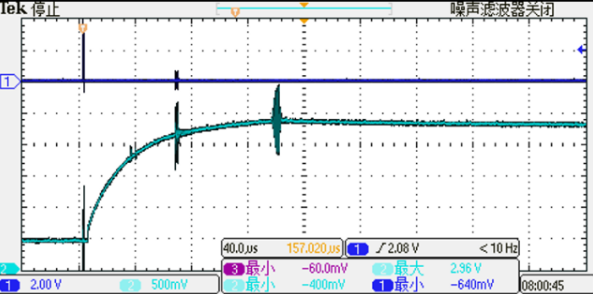

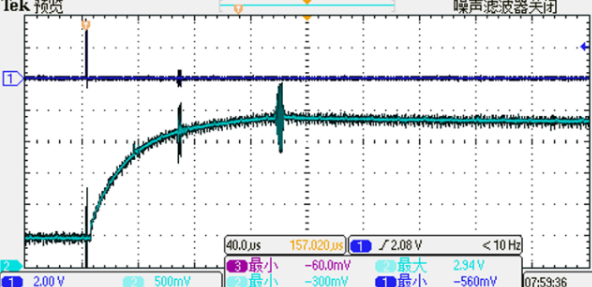

我还对信号有一些问题。 我发现、我自己设计的 COMP-IN 信号在测量周期中呈现出下降趋势、如图所示:

问题2 为什么 VCOM (或 COMP-IN)在测试结束前下降? BTW、为什么我在使用 EVM 时甚至看不到充电过程?

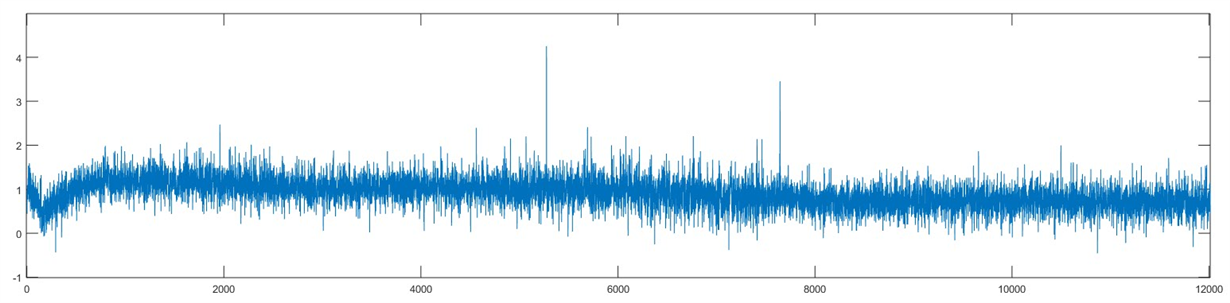

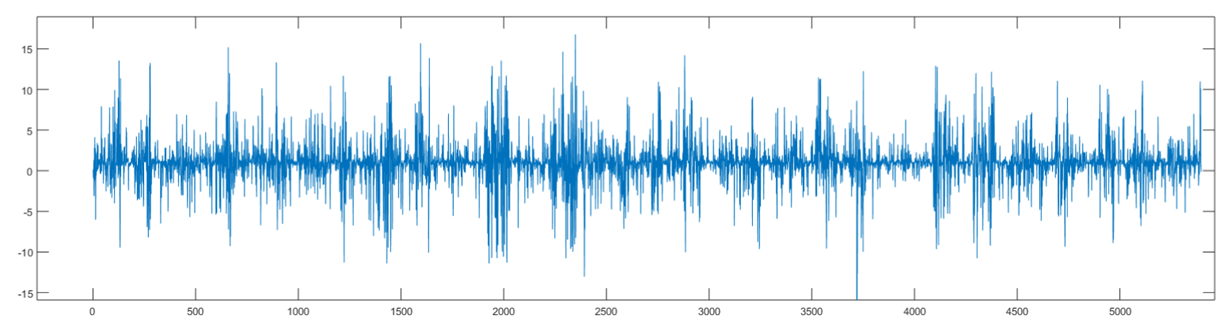

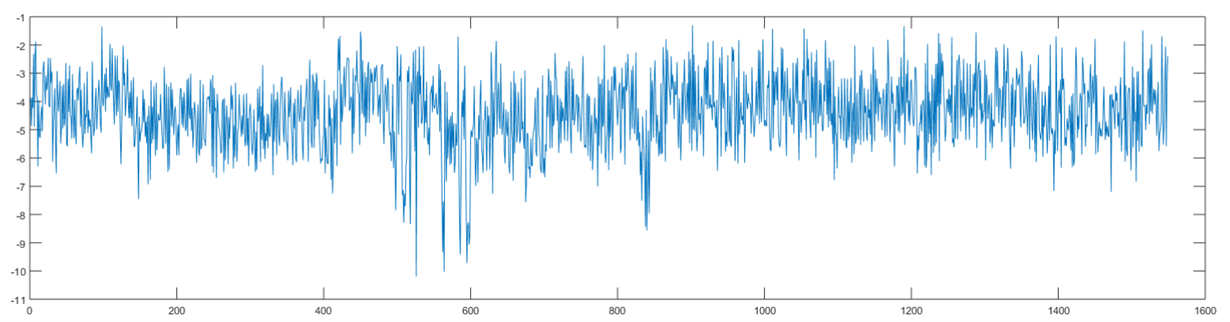

另一个问题是、当我将 电路板的 UART 引脚连接到 TTL 到 RS232转换器(尤其是电源引脚)时、COMP-IN 信号上的噪声将比以前大得多、如图所示:

问题3 我发现噪声来自 VCOM 引脚、但我无法理解原因。 请解释一下。

祝你一切顺利!