主题中讨论的其他器件:DCA1000EVM、

各位专家、您好!

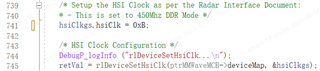

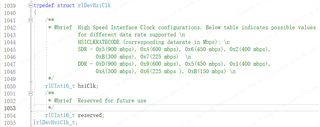

我使用示波 器监控 LVDS 数据速率、发现它是450MHz。 然后、我将 hsiClkgs.hsiClk 设置为0xB 或 mmWave_link_mailbox.c 中的其他值、但 LVDS 数据速率仍然为450MHz、 不是 我想要 的。

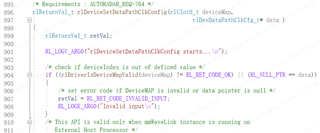

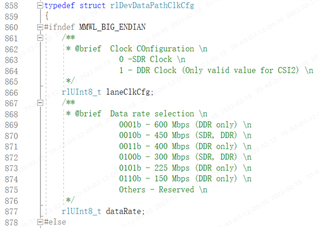

此外、我尝试调用 rlDeviceSetDataPathClkConfig 的 API 来配置 LVDS 数据速率、但 仍然无效、并且 该 API 返回值为-12、似乎 不支持调用的 API。

那么、如何 有效地配置 LVDS 数据速率呢?

非常感谢。