请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMP112 您好!

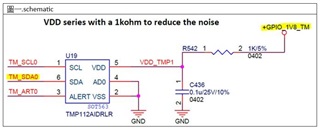

TMP112上电序列、我们现在为 VDD 和 SDA 上拉1.8V 使用相同的电源、如所示

1.系统直接上电后、SDA 管脚会出现毛刺脉冲、如绿色波形所示。 这是由内部逻辑电路未就绪这一事实导致的吗? 规格中没有加电建议。

2.首先为 VDD 提供1.8V 电压,然后将1.8V 电压上拉至 SDA,无干扰。

这有风险吗?

图1:

图2:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.