主题中讨论的其他器件: AWR1843AOP

您好!

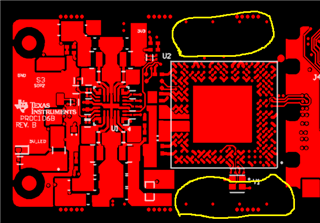

我有关于 AWR1843AOPEVM PCB 的问题。

关于 EVM PCB 的第1层图形、请告诉我为何 AWR1843AOP 周围移除了 GND 图形。

请咨询。

此致、

Shoko

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我有关于 AWR1843AOPEVM PCB 的问题。

关于 EVM PCB 的第1层图形、请告诉我为何 AWR1843AOP 周围移除了 GND 图形。

请咨询。

此致、

Shoko

您好 Shoko-San:

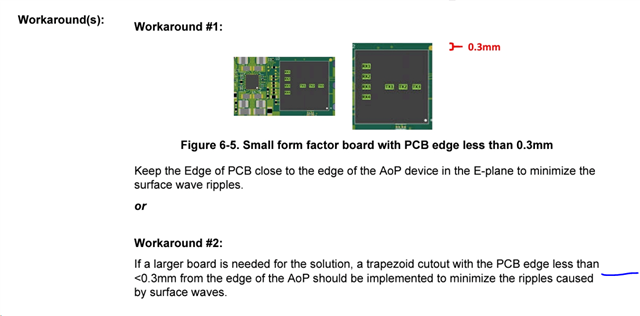

与我的团队进行核实后、我知道这样做是为了消除天线附近的表面波效应。 一般来说、 我们确实建议器件上下不要有 PCB (即使这在参考设计中没有100%遵循、也是一般建议)。

AWR1843AOP 器件勘误表、器件修订版本1.0 (修订版 A)(TI.com)

此致、

詹姆斯