Other Parts Discussed in Thread: TRF1208, AFE7950

主题中讨论的其他器件:AFE7960、 TRF1208、 AFE7950

工具/软件:

尊敬的团队:

我尝试从与 TSW1457EVM 配合使用的 AFE7960+TRF1208 EVM 获取 DAC 输出。

根据我们的要求、我给出了 LMK 时钟在10dBm 时为3GHz、AFE 参考时钟在10dBm 时为12GHz。 EVM 模块的输入电压为5.5V@4A 、FPGA 板 TSW14J57的输入电压为12V@4A 。

但在 Latte 中运行脚本时、会观察到以下附加的错误。

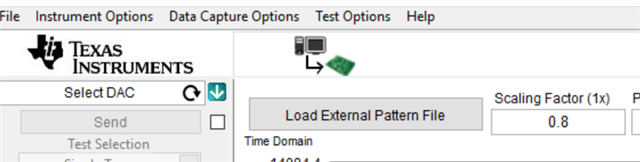

我在 HSDC 中多次尝试点击 DAC 图形的"Send"方法、并运行命令"AFE.adcDacSync (1)"。 但观察到了相同的误差

请为此提出一个解决方案。