工具/软件:

你好

我 使用连接到 Xilinx ZCU102 开发板的 AFE7950EVM 成功实现了“TI ZCU102 8b10b“工程 ZCU102_AFE79xx_8b10b_10Gbps。

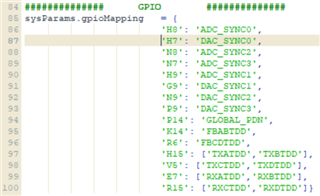

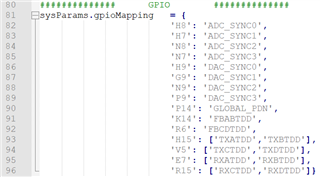

我的设置如下:

FRef = 245.76

FadcRx = 2457.6

FadcFb = 2457.6

Fdac = 2457.6*4.

LMFSHd = 24410

K = 16

LvdsSync= False

fpgaRefClk = 245.76

我修改了一些 IP 来更改 MGT 参考时钟(如 GT 和 PLL)、正确更改了 jesd_link_params.vh 文件和 constraints.xdc 文件。

我遵循 TI204c-Setup.docx:

- 打开 ZCU102 的电源

- 打开 AFE7950EVM 的电源

- 打开 Latte

- 运行 setup.py

- 运行 devInit.py

- 运行 ConfigLmk.py

- 对 FPGA 进行编程

- 释放 MASTER_RESET_n -> 1

- 释放 TX_RESET -> 0

- 运行 ConfigAfe.py

- 释放 RX_RESET -> 0

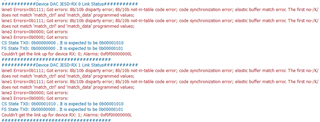

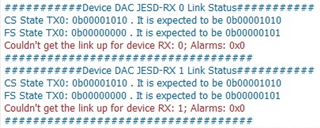

我看到 qpll0 锁定在硬件管理器 VIO1 上、但在 Latte 工具上、我看到 RX 链路存在问题。

我已经在 jesd_link_params.vh 中为 JESD 进行了正确的设置。

`UNDEF LANE_ADC_TO_GT_MAP

`define LANE_ADC_TO_GT_MAP{5、4、6、7、3、0、2、1}

`UNDEF LANE_DAC_TO_GT_MAP

`d微调 LANE_DAC_TO_GT_MAP{4、5、6、7、3、0、2、1}

这可能是什么问题?