主题: LMK04828 中讨论的其他器件

工具/软件:

大家好!

在 雷达和 5G 无线测试仪的高通道数 JESD204B 时钟生成参考设计文档中 、有一个示例介绍了步骤、但没有非常详细的说明。 我想在非常接近 TIDA-01023 参考设计的设置上重复这个示例:多个从设备 LMK04828 由 CLKin0 和 CLKin1 输入由主 LMK04828 驱动。 CLKin1 为 300MHz、CLKin0 为分频器复位信号。

我是否正确地假设它是如何实现的:

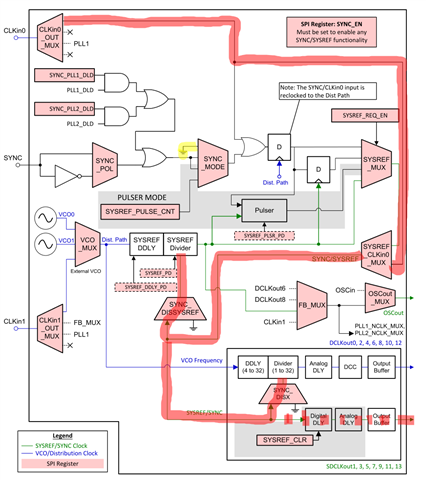

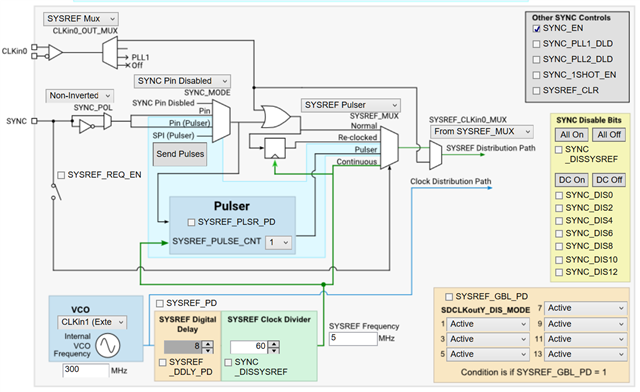

1) 在分配模式下配置从器件、CLKin1 用作时钟分配链输入、CLKin0 被旁路至 SYSREF/SYNC 路径:

2) 将主器件配置为分配模式、将 CLKin1 路由到时钟驱动路径、将脉冲发生器路由到 SYSREF 路径。 在 SYNC 期间也会复位 SYSREF 分频器:

3) 通过 SPI 发送同步事件、因此脉冲发生器会生成 N 个脉冲、从而对齐主 LMK04828 的所有输出

4) 禁用主器件上的分频器同步、并通过将 0 设置为相应的 CLKout_X_(X+1)_PD 位来启用 CLK 输出。 现在、所有从器件都使用 300MHz 高速时钟进行计时

5) 通过 SPI 发送同步事件、因此脉冲发生器会生成 N 个脉冲、从而对齐从 LMK04828 器件的所有分频器

6) 每个从器件将 SYSREF 多路复用器输入更改为连续、现在输出与 SYSREF 信号对齐的高速时钟信号、所有从器件都彼此具有确定性延迟。