主题中讨论的其他器件: TPS552882、 TPS25940

我正在考虑基于 PMP9766的5Vmain/6A、300ms 备份时间条件的备份解决方案。

(降压/升压 IC 将更改 TPS552882、VCF:4.75V)

请告诉我以下关于 PMP9766解决方案的两点:

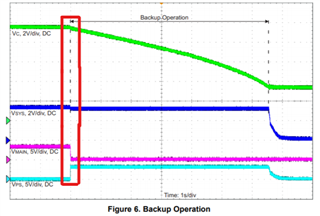

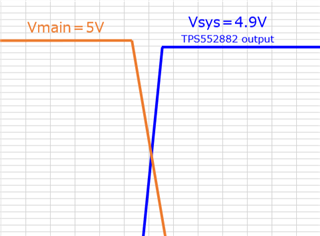

Δ V ①I 、将 Vmain 更改为降压/升压 Vout 的时序存在一些延迟和冲突、设计指南和缩放图像如下所示。

・当碰撞时间变长时,是否有任何问题或注意事项?

如果有问题、请告诉我任何措施。 (断开 FET 是否添加到 TPS552882输出电压侧(R6至 C4之间)、有效?)

・假设低于图6的时间有多长?

②When Vmain 下降并将降压/升压输出更改为 VSYS、TPS25940A 是否应设置为禁用?

如果应禁用、我计划通过添加分压器将 Vmain 设置为小于 VCF =小于 UVLO 阈值、这是否正确?

此致、

Satoshi