主题中讨论的其他器件:MSP430F5152、

工具/软件:Code Composer Studio

您好!

我将使用基于 TIDA-00120参考设计的 MSP430F5152开发 MPPT 控制器。

将设计从最初的插式降压 转换器调制为单通道 降压转换器。

为了确保适当的死区时间、 我 在使用参考计时器 D 初始化例程时将 T1CCTL1和 T1CCTL2的值差设置为25

应用 MC_3向上向下计数模式。 然后、我发现 PWM 死区时间正在从几乎50ns 更改为1.x us、而没有任何 S/W 参与。

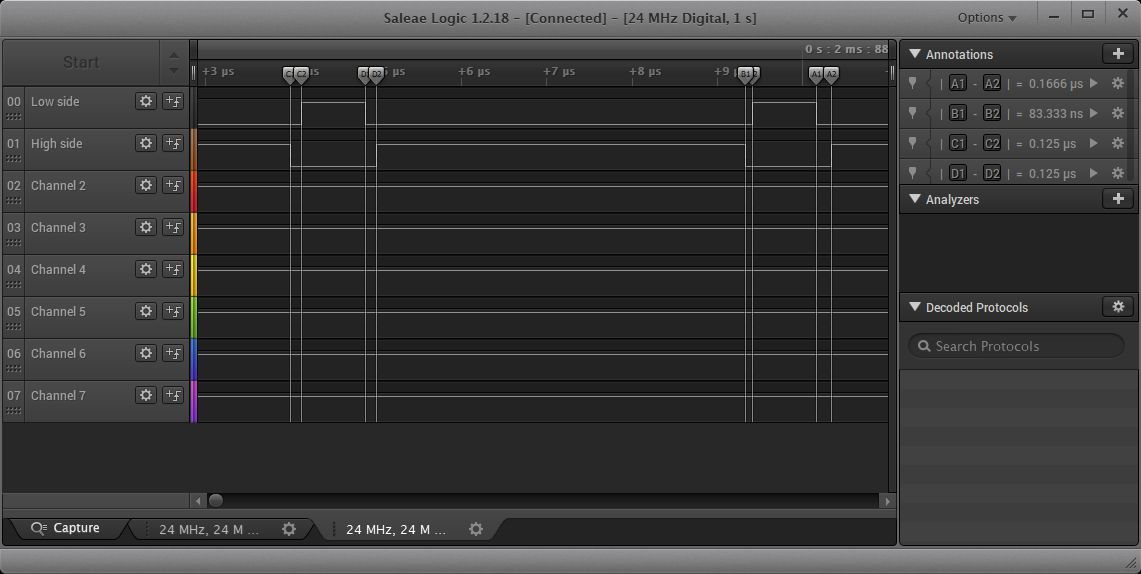

我在 断点停止条件下使用示波器和逻辑分析器测量 PWM 波形、在 256MHz 的 tmer D free 运行模式下。

Somtime 死区时间几乎变为 50ns 、有时变为 1.x us。 当然、如果我将 T1CCTL1和 T1CCTL2的值间隔设为40、

这有点安全。 但它可能 会增加 低侧体二极管的导通损耗、 我想尽量缩短死区时间。

为什么 即使在 CCS 中的断点停止条件下也会更改占空比时序?

下面是 我应用的 TimerD 初始化路由。 我还连接 了简单的逻辑分析仪测量的波形。 逻辑分析仪仅用于24M 样本。

捕获的 LSB 误差约为40nsec。 但当我在示波器中测量时、显示的条件几乎相同。

--------------------------------------------------------------------

空 Init_Timer (空)

{

struct s_TLV_Timer_D_CAL_Data * pTD0CAL; //在 tlv.h 中初始化结构

unsigned char bTD0CAL_bytes;

// unsigned int i = 20;

//将 TimerD 配置为高分辨率自由运行模式

get_TLV_Info (TLV_TIMER_D_CAL、0、&bTD0CAL_bytes、(无符号整型**)&pTD0CAL);

//Get TimerD0校准值(实例0)

if (bTD0CAL_bytes = 0x0)

{

//未找到 TimerD 自由运行校准数据

while (1); //此处循环

}

//配置主计时器实例- TimerD0、高分辨率校准模式

TD1CTL0 = TDSSEL_2; // TDCLK = SMCLK = 25MHz =高分辨率输入时钟选择

TD1HCTL1 = pTD0CAL->TDH0CTL1_256; //读取256Mhz TimerD TLV 数据

TD1CTL1 |= TDCLKM_1; //选择高分辨率本地时钟

TD0HCTL0 = TDHEN + TDHM_1; // calen=0 =>自由运行模式;启用高分辨率模式

TD1HCTL0 = TDHEN + TDHM_1; // calen=0 =>自由运行模式;启用高分辨率模式 // TDHM_0 => 256Mhz、TDHM_1 =>256Mhz

//此处、Timer D 配置为以256Mhz 运行

TD1CCR0 = 700; // 256M 向上向下/700 = 182.8Khz 是降压级的工作频率

TD1CCTL0 |= CCIE; //中断被使能以调整相位

TD1CCR1 =占空比; //低侧 PW_L2? 高侧 PW_H1 *****

TD1CCTL1 |= OUTMOD_2; // TD0CCR1,复位/置位(outmode2->切换和复位?)

TD1CCR2 = Duty; // Dute-25被完成来提供死区。 高侧 PW_H2。 PW_L1

TD1CCTL2 |= OUTMOD_6; // TD0CCR2、设置/复位

TEC1XCTL2 |= TECAXCLREN; //通过启用从机计时器的辅助清零来启用同步清零

TD1CTL0 |= MC_3 + TDCLR; //向上/向下计数模式、清除 TDR、启动计时器-向上/向下-由 YSK 修改

}

#pragma vector=Timer1_D0_vector

_interrupt void Timer1_D0_ISR (void)

{

TD1CCTL0 &=~CCIE;

PHASE_PHASE_PHASE_DONE = 1;

}

#pragma vector=Timer1_D1_vector

_interrupt void Timer1_D1_ISR (void)

{

switch (__evo_in_range (TD1IV、30))

{

情况 0:中断; //无中断

情况 2:中断; //未使用 CCR1

情况 4:中断; //未使用 CCR2

情况 6:中断; //保留

情况 8:中断; //保留

情况10:中断; //保留

情况12:中断; //保留

案例14:中断;

案例16:中断;

案例18: //时钟失败低电平

while (1); //输入参考时钟频率过低;请在此处陷阱

案例20: //时钟高电平失败

while (1); //输入参考时钟频率过高;请在此处陷阱

案例22: //高分辨率频率已锁定

//高分辨率频率已锁定;现在配置端口以在 TD0/TD1上输出 PWM

P1SEL |= BIT7; // P1.6/TD0.0、P1.7、TD0.1、选项选择

P1

DIR |= BIT6 + BIT7; //输出方向

P2SEL |= BIT0 + BIT2 + BIT3; // P2.0/TD0.2、P2.1/TD1.0、P2.2/TD1.1、P2.3/TD1.2、 选项选择

P2DIR |= BIT0 + BIT2 + BIT3; //输出方向

_BIC_SR_REGISTER_ON_EXIT (LPM0_Bits + GIE); //返回 main 时退出 LPM0

中断;

案例24:中断; //高分辨率频率未锁定

情况26:中断; //保留

情况28:中断; //保留

案例30:中断; //保留

默认值:break;

}

}

TD1CCTL1 = OUTMOD_2; // 输出模式

TD1CCTL2 = OUTMOD_6; //输出模式

--------------------------------------------------------------------

非常感谢您的建议!

YS Kim