主题中讨论的其他器件:TINA-TI

工具/软件:TINA-TI 或 Spice 模型

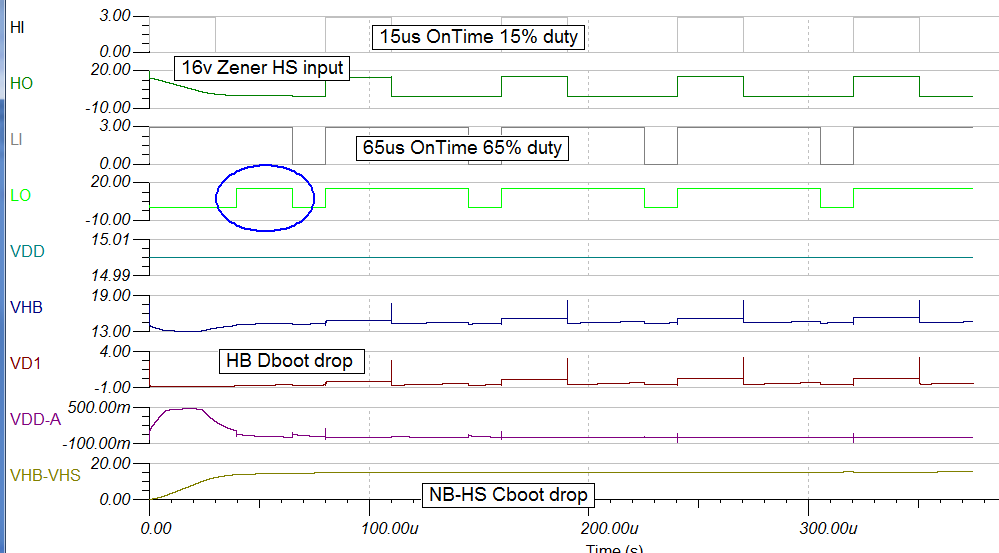

HS 引脚从 HO 引脚传递1/2电桥高电压并 在 HS 引脚上添加16V 齐纳二极管时压缩绘图输出中的 HO 信号的问题。

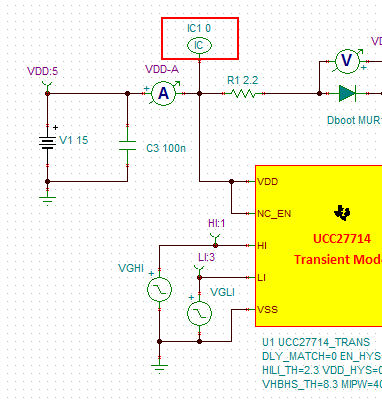

HS 引脚 被连接至 高侧 NFET 源极、从而在 低侧 NFET 上进入漏极、1/2电桥 布局。 当 两个信号发生器在不同占空比下将驱动信号生成到 HI/LI 输入中时、LO 输出中也会显示初始红色脉冲(蓝色椭圆形)、周期为80us。

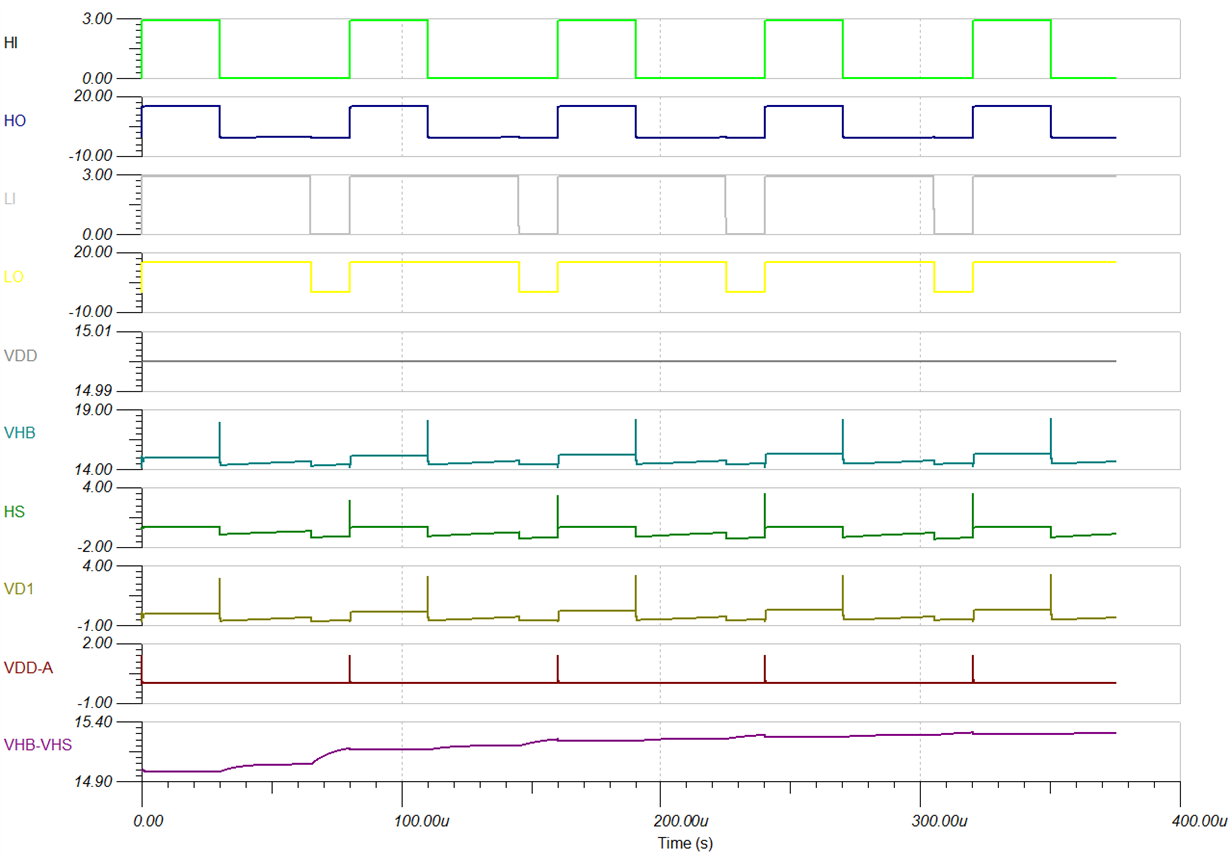

HS 引脚是否 预计会在生产芯片中将高电压输出 HO 引脚(未显示+160V)?

是否有什么想法会导致 HO 输出产生 如下 捕获所示的初始红色脉冲?

谢谢、