主题中讨论的其他器件:TINA-TI、 LM25116

工具/软件:TINA-TI 或 Spice 模型

(请勿告诉我使用 WebBench、TINA Spice 等。)

(一般情况下,请不要仅使用有关“如何解决收敛错误”的链接进行回复。)

注意:我离 Spice 专家还很远。

TLDR -我正在使用 (嗯、尝试使用)未加密修订版 C 瞬态 Spice LM5116模型。 我已经修改了模型的语法、使其运行时不会出现语法错误、但目前、我仍然遇到几百微秒的"时间步进过小"错误。 在此仿真时、控制器开始进入 DCM、LO 会松鼠(这是一个技术术语)尝试确定何时关闭底部 FET。

在我对 Spice 的了解有限的情况下、我看到该模型使用 if 语句来驱动 HO 和 LO 引脚、这些引脚进而驱动 FET 栅极、进而迫使 Spice 仿真器降低其时间步长以解决突然的非线性转换、 进而会产生收敛错误(即"时间步长太小")。

无需赘言、但使用简单的逻辑 IF 语句对输出 HO 或 LO 引脚进行建模并不符合 LM5116的数据表规格。 有人可以解决这个问题吗?

下面是完整的背景信息:

我实际上想使用 LM25116模型。 我为 LM25116下载了未加密修订版 A 瞬态 Spice 模型 、该模型在 LTSpice 17中立即无法使用。 我在模型内部的节点处发现了初始"无法找到操作点"的错误。 它可以是节点 U1:_s1_mod-instance s:U1:1、也可以是节点28。

我尝试了所有正常的调试步骤:

- 给出了电容器 ESR 值

- 放宽电流/电压/相对容差

- 减少最大时间步长

- 添加初始节点电压(例如、在输出端)

- 在每个节点上添加一条通过高阻值电阻器接地的路径

- 在几百微秒内升高输入电压

- 告诉 LTSpice 只需使用 UIC 语句忽略初始操作点。

最后一个帮助有点小、但在某个间歇时间大于0 (通常仿真中只有几十或几百微秒)时、仍然会有一个"时间步长太小"错误(同样、我假设某个东西不会收敛)。

我联系了 TI 电子邮件支持、告诉他们使用另一个非 LTSpice 仿真器不在范围内、他们向我发送了:

因此、我为 LM5116下载了未加密修订版 C 瞬态 Spice 模型 、在 LTSpice 17中也立即无法使用。 不过、这会更好一点、因为它似乎更一致地通过了初始运行条件、而我不必使用忽略初始运行点(UIC)语句。 在中、它仍然导致了几微秒的"时间步进太小"错误。 支持和 FAE 建议放宽特定容差参数(我在上述调试步骤列表中提到)。 这使我足够远、我可以从 LTSpice 中看到有关语法的错误日志、在 LM5116模型中它显然无法理解。 具体而言:

- LTSpice 不理解如何使用 tilde ~字符作为语法。

- LTSpice 不理解双曲括号{parameter}}的使用。 单个曲括号为精细{parameter}、但不是双曲括号{parameter}}。

我的研究表明:

1. tilde ~似乎是 Spice 模型中不能普遍识别的语法。 它在 LM5116模型的第488行中使用一次、在 if 语句中具有"greater than "(大于)>。 我删除了它、将"greater than (大于)">替换为"less than (小于)"<、并且 LTSpice 给出的语法错误消失了。

2.双曲括号用于控制如何在 Spice 语法中计算参数。 我看不到使用了双尖括号、就像普通程序员一样、我认为它们可能是多余的。 我将所有对双曲括号的引用替换为单个曲括号-语法错误 LTSpice 已消失。 LM5116模型中的两个双卷括号成对出现在以下行中:500/501、622/623、626/627、632/633、639/640、 664/665、671/673。

问题1: 是否有人可以确认上述两项对模型语法的更改是否良好? 或者、如果它们影响模型、如何?

因此、随着语法错误的消失、仿真运行得更快、但仍然存在间歇性收敛故障(即、"timestep too small" at times >0)。 但是、现在我相信我确定了这些"时间步长太小"错误何时发生-毫不奇怪、我们是在打开和关闭 FET 时发生的。 SPICE 仿真器已经很难计算 FET 等非线性器件的导通和关断时间-当 LO 引脚决定每隔一个时间步长更改其输出(LO 在 ps 或更短的时间内从导通变为关断)时、这会使计算变得更加困难。

我的条件只是一个基本条件:

- VIN 在150us 内从0v 上升到8v (或16V)、以及

- 轻负载电流为1mA 或100mA、在500us 时开启。

- 正如我提到过的、CS 和 GND 之间的电流感应电阻器

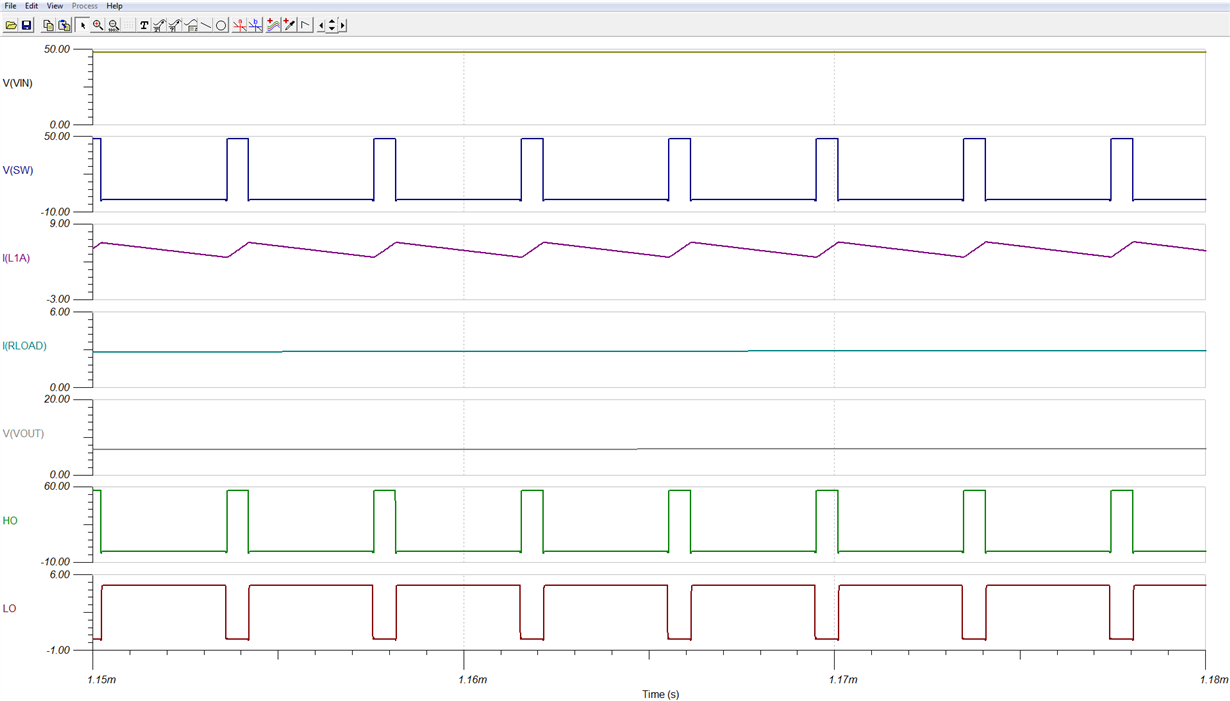

VIN 完成斜升后、我看到 LO 引脚切换非常不稳定。 它在 LO 的上升沿和下降沿发生、但在下降沿尤其糟糕。 它在转换器从 CCM 转换到 DCM 时开始、并在 DCM 期间继续、无论轻负载是否以500us 的速度开启。

此 LO"抖动"迫使 Spice 降低时间步长并导致收敛错误(即、我认为"时间步长太小")。

切线:支持人员还向我发送 了此链接 、该链接似乎与我正在观察的本低"抖动"问题无关。 但是、如果任何人在了解如何调整 TINA 参数以使方形边线看起来更平方时需要帮助、该链接可能会有所帮助。

回到 LO 抖动、我在修订版 C LM5116模型中看到了这一点:

- 第77行显示了 CS 引脚和一些内部节点39之间的1 Ω 串联电阻

- 第87行显示、节点39由任意电压源定义

- 第89行显示了由 if 语句定义的任意电压源。

我猜、该 IC 特殊 VRAMP 功能的逻辑更易于使用逻辑 IF 语句建模...但是、当您使用逻辑 IF 语句驱动连接到现实世界的引脚时、不会对现实世界行为建模。

为了证明这是问题所在(部分是我自己的问题)、我查看了 LM5116数据表、其中指出、在1000pF (1nF)负载的测试条件下、HO 和 LO 引脚具有10-20ns 范围内的典型上升/下降时间。 因此、我在 LO 节点上悬挂了一个1nF 电容器(与具有小得多的 CG 的低侧 FET 并联)。 我在 LO 节点观察并测量了相同的抖动、上升/下降时间为 ps 和低于 ps。

据我所知、我的电路中导致 LM5116开始该 LO jitterityness 的关键因素是、进入 CS 引脚的感应电阻器电压(节点称为"感应")此时将在负值和正值之间转换。

- 负值表示电流从 GND、经过 Rsense、流经电感器、流向负载(通常是我们期望的值)和

- 正值表示电流从负载流过电感器、通过 Rsense 流至 GND (不是我们想要的-降低效率-此时关闭 LO 引脚是很有意义的。)

但是、由于 CS 在-UV 至+UV 值的一段时间内在零附近徘徊、因此 LM5116模型的 if 语句将这些轻微的-至+转换解释为急剧转换、然后指示 LO 引脚从导通切换到关断(或反之)非常快。 这会导致收敛错误。

我尝试通过以下步骤来平缓 CS 引脚侧的-至+转换、但这些尝试未成功。 底线是 LO 引脚不会对数据表所需的模拟行为建模。

问题2: 有人可以解决这个问题吗?

我尝试解决此问题的其他调试步骤:

- 在电流感应电阻器中添加了~40pH 串联电感器、以尝试降低 jitteryness。 没有帮助、因为这不是让人产生 jitteryness 的原因。

- 为电流感应电阻器添加了并联~600nF 电容器、以尝试降低 jitteryness。 没有帮助、原因与上述相同。

- 尝试查看模型并查看是否存在一些迟滞、我可以轻松地将其应用于 CS 输入。 没有这样的开关、我可以看到附加迟滞参数显然会有所帮助、因为该引脚的功能与该器件的其他斜坡特性相结合。

请注意、有一个点有开关节点谐振振铃、但这与此问题无关。 LM5116数据表中提到了开关节点振铃、因此它是模拟(即实际)效应、是在我的仿真中预测的。 根据数据表的建议、我在开关节点上添加了一个缓冲电路、该电路消失了。