主题中讨论的其他器件:TINA-TI、

工具/软件:TINA-TI 或 Spice 模型

您好!

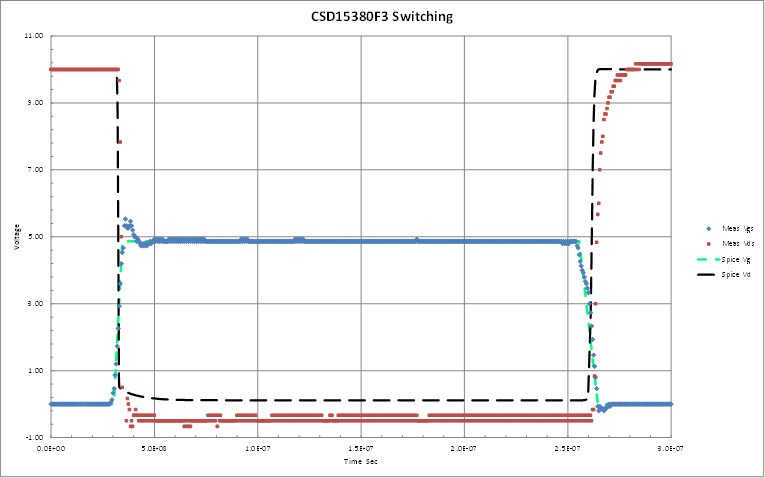

我已占用 FET (CSD15380F3)的上升/下降时间。 但仿真结果和数据表规格不同。

在数据表中、测试条件为 VDS=10V、Vgs=4.5V、Rg=0Ohm、Ids=0.1A。 上升时间为1ns、下降时间为7ns。

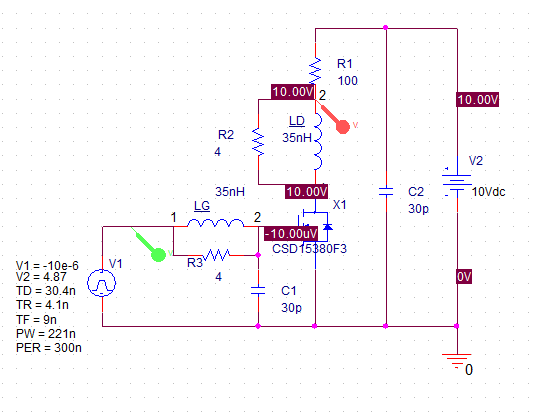

因此、在仿真中、我 分别将0Ohm 和100Ohm 连接到 FET 的栅极和漏极。 Vds 为10V、Vgs 为4.5V 脉冲。(我将 Vgs 的上升/下降时间设置为1ps。)

但在我的仿真结果中、上升时间为1.6ns、下降时间为1.6ns。

我的仿真设置有什么问题?

如何仿真 FET 的上升和下降时间?