主题中讨论的其他器件: UCC28700

您好!

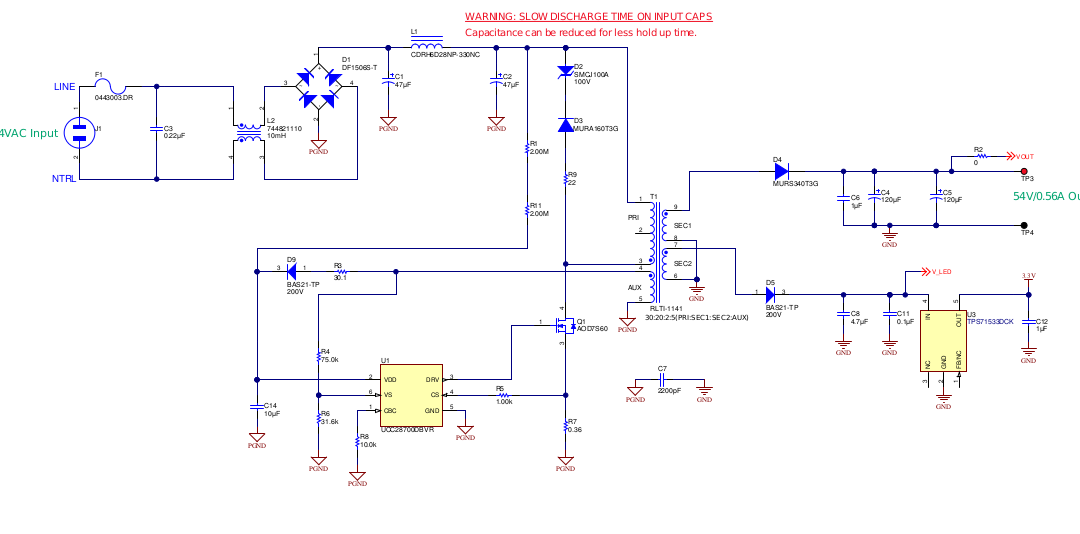

在 TP3和 TP4上测量的输出电压中、纹波约为12V。 其范围为57V 至45V。 此外、在 T1的第二2级、电压范围为3.6V 至0V。 关闭时间约为500ms。 我认为 UCC28700将进入欠压锁定(UVLO)状态。 所有值和器件与原始基准电路(PMP20199)保持不变。

在 UCC28700数据表中、CVDD (C14)的建议值为0.047uf 至1uf、根据我的计算、RLC (R5)应为2.89k Ω。

此外、如果我对电路进行以下更改、还请告诉我会发生什么情况:

1.使 C14 = 1uF。

2.更改 R5 = 2.87k 欧姆

3.将 R3的值从30.1k 更改为75k。

请建议我如何调试该板。

提前感谢您。