工具与软件:

团队成员、您好!

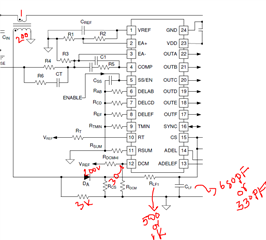

当我们尝试根据参考设计、使用我们自己的定制设计运行具有 CV 调节的 PCM 控制时、我们正在观察 C 和 OUT D 占空比结果事件、但我们已将所需/计算/推荐的电路输入初级 CT 电流检测路径中、如下所示。

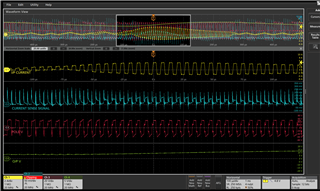

我们已扩展输入电压板启动了 RFLT 和 CFLT 变化的两种情况、如所示 案例1:500 Ohm 和680pF 和 案例2:1k Ω 和330 pF (Fcutoff 高于 FSW-150kHz)

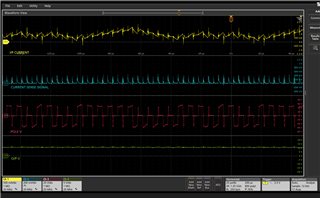

案例1:

运行条件;输入电压50V、输出电压10V、输出电流0.5A

运行条件;输入电压50V、输出电压10V、输出电流4A

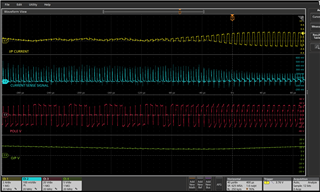

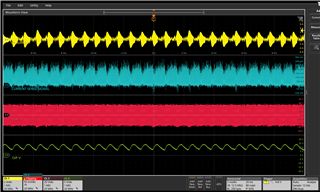

案例2:

运行条件;输入电压50V、输出电压10V、输出电流0.5A

运行条件;输入电压50V、输出电压10V、输出电流4A

您能否告诉我们如何提高电流检测反馈的抗噪性、以便避免如 PRI 极点电压所示的高于和低于50%的 OUT C 和 OUT D 占空比变化。

补偿器输出跟随输出电压中所示的纹波电压 (接近1.1V (+/- 0.1V))、但没有急剧摆幅。

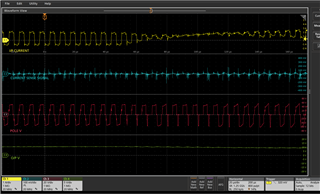

正如其他输入一样、我们通过移除 pri CT 反馈信号进行了实验、但仍观察到 OUT C 和 OUT D 中类似的占空比变化 、如下所示:通过 PRI 极点电压、Vout 调节为设定基准。

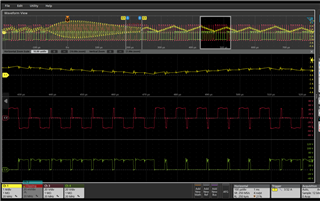

在下面的波形中、CH3显示了初级极电压、而 CH4 QD 漏源电压(OUT D)显示桥臂2 (OUT C 和 OUT D)的占空比变化问题