工具与软件:

我正在使用 UCC28740-Q1设计一款反激式器件。

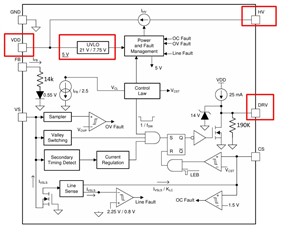

此 IC 包括 HV 引脚、用于提供在启动期间为 IC 的 VDD 充电的路径。 但是、在对 VDD 引脚充电至导通电平(CH2达到21V)后、我仍然看不到生成的任何 PWM 脉冲。

可能会出现什么问题? 可能的任何保护?

CH1 = VGS、CH2 = VDD、CH3 = VHV、CH4 = VOUT

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

我正在使用 UCC28740-Q1设计一款反激式器件。

此 IC 包括 HV 引脚、用于提供在启动期间为 IC 的 VDD 充电的路径。 但是、在对 VDD 引脚充电至导通电平(CH2达到21V)后、我仍然看不到生成的任何 PWM 脉冲。

可能会出现什么问题? 可能的任何保护?

CH1 = VGS、CH2 = VDD、CH3 = VHV、CH4 = VOUT

何敏堂

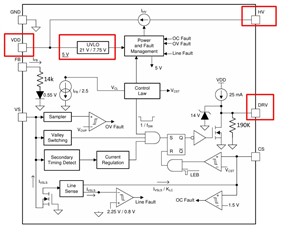

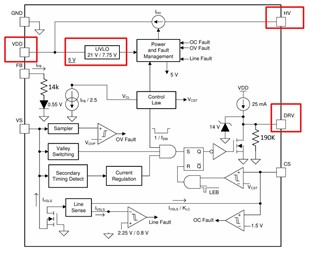

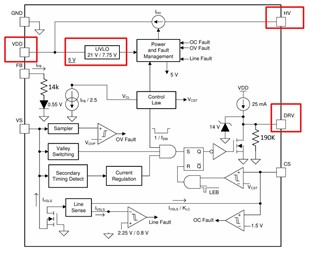

-首先,请分享原理图和变压器参数。

-Secondly,请在示波器中显示以下波形:(GND-GND) VDD、 (DRV-GND)、 时间刻度为~10us/div 的(CS-GND)、因此我可以检查 DRV 脉冲以及 VS 和 CS、以检查是否存在任何故障。 将触发器开启(UVLO_GND)通道、上升 VDD (21V)

-根据(UVLO-GND)波形,控制器处于故障模式(在 VDD 开关之间上升和下降),所以我们需要检查触发了什么故障,并查看原理图,将故障与原理图中的任何组件故障或错误联系起来。

-最后、当(PWM-GND)达到 UVLO_ON (21V)时、控制器始终在(DRV-GND)处发送3个 VDD 脉冲以检查是否存在任何故障、如果有任何故障(通过 VS 和/或 CS VDD)、(PWM-GND)将降低、直到达到 UVLO_OFF、然后尝试重新启动以寻找要清除的故障。 如果情况不是这样、那么调试器将一直上升和下降、直到故障被清除。

谢谢你