请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:PMP22650 工具与软件:

我在探索 CLLLC 的控制环路、我有一些疑问。 请帮我澄清一下。

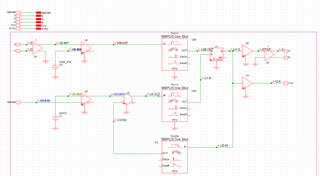

在 CLLLC 的次级侧、有一个名为的块 简单的 SR 驱动器 连接在每个次级侧 MOSFET 的漏极和源极之间。 在该块内部、VSD_ON、IOFF 基准的逻辑是什么? 为什么将其值1V 和5A 用作基准?

2.在 IOFF 比较器中、IOFF 连接在比较器的同相引脚上。 因此、在大于5A 的检测电流下、输出应为逻辑低电平、但在这种情况下、其行为方式会有所不同。

请找到随附的屏幕截图。