工具与软件:

您好!

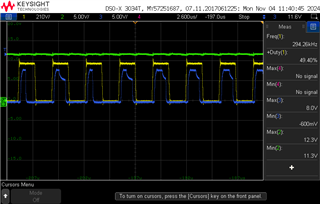

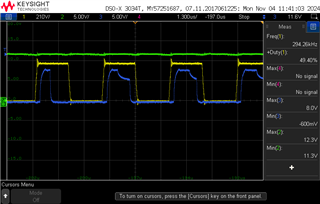

正如我在上一主题中提到的、驱动 FET 栅极的 VG 引脚电压过低(约为8V)。 我测量了 VDD、电压范围是11.3V 至12.3V。 参考下面的测量图像。

您是否认为此问题可能是因为 REG 电容不够(2.2uF)? FET 的 Rdson 是否会改变控制器的行为?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

FET 关断的栅极基于 IDs*Rdson。 如果 IDS*Rdson <-50mV、则栅极电压应为最大值。 当 VDS 下降至-50mV 时、FET 栅极将调整 FET 栅极电压、以调整 FET 阻抗。 一旦无法保持-50mV 的电压且 VDS 超过- 10mV、FET 就会关断。

问题是栅极电压大约为8V。 这不应该发生。

我还没有看到这个栅极驱动器出现这种情况、或者听说过其他任何人抱怨这个问题。 您能否仔细检查探头的校准、以确保实际测量的是8V PEAK?

如果这是真的、可能导致这种情况的原因是 FET 负载极高、或者 UCC24624的 RETURN 和 VS 之间存在较大压降。 您曾提到、您直接在 VG 的 VG 和 VS 上检查此值、因此不应该是这种情况。

第二种可能情况是 UCC24624的结温高于绝对最大额定值。

您可能需要检查结温、以查看温度是否过热。

第三种可能情况是栅极驱动器尝试驱动超过1.5A 的电流。 如果是这种情况、负载将导致栅极的运行电流低于数据表中的规定值。 因此、您可能需要检查这一点。

最后一个建议是、确保 VDD 电容器至少是您尝试驱动的 FET 栅极电容的10倍。 否则、可能会导致栅极电压也无法驱动那么高的电平。

此致、

感谢您提供这些信息。 目前、我使用的设计需要小的 Rdson (0.7 m Ω)、并且每个 FET 上运行的电流约为20A。我注意到了一些问题、这也可能是导致此行为的原因。

1) 1)目前、我的设计在 Rg 和 VSS 之间没有下拉电阻器。 这可能会导致栅极电压出现一些问题。

2)控制器的 VSS 与负载电流流经的同一接地共享、此时我有100A 以上的电流流流过系统。

3) 3)因为我有矩阵变压器配置(3个变压器串联并联)、并且每个变压器都有自己的 UCC24624 (总共3个)、我注意到只有1个变压器的加热速度高于其他变压器(差异接近25摄氏度)。 这可能是由于设计中的一些寄生效应、也可能是由于2)中提到的原因。

在1kW 测试期间、UCC24624的温度约为61°C、因此我认为结温可能远高于最高温度。 目前 VDD 电容器的电容为1uF、是 FET 栅极电容的10倍(如果我考虑 Cgs = Ciss - Crss)。

我将尝试再运行一些测试。 再次感谢大家。