请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMG3422R030 工具与软件:

尊敬的团队:

感谢您对我先前的问题的答复。 根据您的建议和进一步的实验、我提出了以下观察结果并进行了进一步澄清:

- 双脉冲测试问题

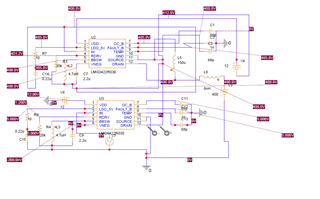

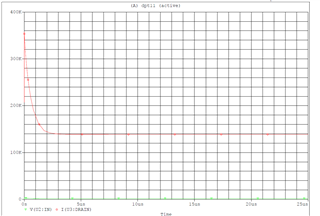

我已经附上了我的原理图以及 Vds 和 ID 的结果、供您参考。 根据 LMG342xx 主板原理图、我复制了该设置、并在 LDO 引脚处添加了一个与0.22 µF 电容串联的10欧姆电阻器。 遗憾的是、我仍然无法实现预期的双脉冲测试结果。 您能否回顾一下设置并就可能需要的任何其他更改提供建议? - 使用自举降低压摆率

关于通过使用顶部 FET 的 FAULT 信号导通 Q1 MOSFET 来降低低侧器件压摆率的方法:- 当 MOSFET 导通时、RDRV 引脚上的有效电阻会降低、这在理论上可能会再次提高压摆率。

- 您能否说明一下、尽管有效电阻发生了变化、但这种方法是如何有效降低压摆率的?

- 将数字隔离器用于 H 桥

对于 H 桥配置、我打算对两个顶部开关的栅极脉冲使用相同的数字隔离器。 考虑到这些器件的不同开关节点、这种方法是否可行? 如果不能、您能否建议采用适当的隔离器配置?

非常感谢您就这些事项提供指导。 如果需要任何其他信息来帮助解决这些问题、请告诉我。

谢谢、此致

b Raja Sekhar