工具与软件:

尊敬的团队:

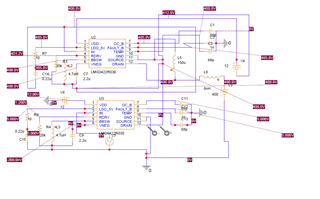

我目前使用同步降压评估板与 LMG3422R030 GaN FET 合作、我面临一些需要帮助的问题。 下面是我的问题的详细信息:

- LDO 引脚连接问题:

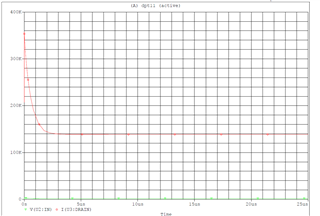

- 当我通过一个与0.22 µF 电容器串联的10欧姆电阻器连接 LDO 引脚时、我无法获得预期的仿真结果。 您能否说明在此设置中是否需要其他注意事项或配置才能正常运行?

- 或者、当我按照数据表将 LDO 引脚连接到5V LDO 输出时、我应该观察到100 V/ns 的压摆率。 但是、电路未按预期工作。 您能否提供有关解决此问题的指导?

- 了解 Q1低侧开关:

- 我想要详细说明位于低侧的 Q1开关如何帮助降低导通期间低侧开关的压摆率。 我无法完全掌握基本机制、因此如果有任何澄清、我会非常感激。

- 适用于 H 桥高侧开关的隔离器:

- 您能建议是否在 H 桥拓扑中将同一个隔离器用于两个高侧开关吗? 如果是、是否有任何我应该注意的特定设计注意事项或限制?

非常感谢您协助解决这些问题并提供必要的澄清。 如果您需要有关电路或仿真设置的其他详细信息、请告知我。

此致

b Raja Sekhar