请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CC1310 大家好、

电源1.9V。 电源模式使用内部直流/直流模式。

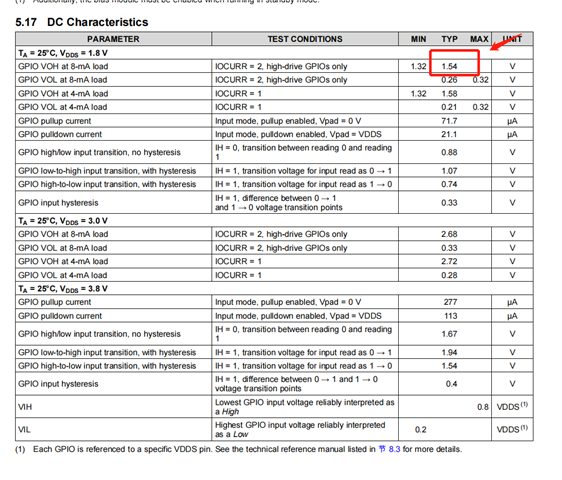

在当前测试期间、DIO5被拉高、发现 DIO 电平为1.9V。 在重复加电断点测试期间、特定的可能性是、DIO 电平只拉高至1.44V。 根据手册的第29页、当提供1.8V 电压时、输出电压应该大约为1.54V。

1) 1)通常、IO 端口的输出电平应与其输入电平相关。 为什么 DIO 输出电平比输入电平低大约0.3V?

2) 2)如果输出电平按照手册在1.44V 正常、为什么 DIO 会被拉高至1.9V?

您能帮助检查这个问题吗? 谢谢。

此致、

樱桃