工具与软件:

您好!

我需要使用 CC1120在可变数据包长度模式下发送大于128字节的数据包。

我已按如下方式设置 GPIO:

- GPIO0配置为 GPIO0_CFG = 0x00。 上升沿中断设置标志"RxFifoThresholdExced"

- GPIO2设置为 GPIO2_CFG = 0x06。 下降沿中断设置标志"RxTxEndOfPacket"

下面的代码适用于低于#define RX_FIFO_THRESHOLD_SIZE (设置为120)的数据包长度

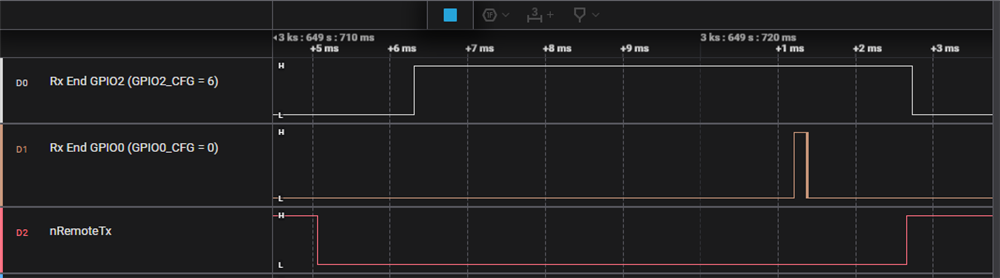

我无法解决的问题是 CC1120 GPIO0线路上偶尔会出现毛刺脉冲。

下图显示了这些问题。 毛刺脉冲信号直接在 GPIO0输出上获取。

CC1120上的不同 GPIO 输出是否存在任何限制?

我已经在这上面呆了几天,我是不知道的想法。

下面:红色低电平表示远程 Tx 正在发送

这是 GPIO0低脉冲的特写

代码:

/**********************************************************************************************

* Function: CC1120_ReceiveData

* Purpose: Receive a packet of FSK data. Manage FIFO to ensure no overflow occurs.

* Max Packet size is 255 bytes (less 2 if PKT_CFG1.APPEND_STATUS enabled)

* Return: 0 for timeout or no invalid CRC etc.

* 1..255 indicating packet size

//Setup GPIOx for rising edge interrupt on RXFIFO_THR.

**********************************************************************************************/

u8 CC1120_ReceiveData(u8 *pData)

{

u8 * pBuffer = pData;

u8 length = 0;

u8 BytesRemaining =0;

u32 startTime = HAL_GetTick(); // Get the current system tick

RxRssi = 0;

RxLqi =0;

RxCrcOK = 0;

CC1120_Strobe(CC1120_SIDLE);

// Reset RxFIFO IFF overflow, underflow

if (CC1120_ReadRegister(MODEM_STATUS1) & (MOD_S1_RXFIFO_OVERFLOW | MOD_S1_RXFIFO_UNDERFLOW ))

{

CC1120_Strobe(CC1120_SIDLE); // Must be in idle state

CC1120_Strobe(CC1120_CMD_SFRX); // Flush RX FIFO. Places CC1120 into IDLE mode

CC1120_Initialise(); // Reinit device

Println("RxFIFO flushed", RED);

RxFifoThresholdExceeded = FALSE;

RxTxEndOfPacket = FALSE;

}

CC1120_ReadRegister(NUM_RXBYTES); // ****** "NUM_RXBYTES or RX_LAST should be read before strobing SRX" *******

CC1120_Strobe(CC1120_CMD_SRX); // Put into RX mode

while(1) // Now receive the data

{

// Case 1: FIFO threshold is exceeded (set by rising edge on GPIO0. GPIO0_CFG = 0)

if (RxFifoThresholdExceeded ) // Flag set by RISING edge from CC1120 GPIO1 - Set as GPIO0_CFG = 0

{

RxFifoThresholdExceeded = FALSE;

// If the length byte hasn't been received yet, read the packet length

if (!length)

{

length = CC1120_ReadRegister(CC1120_FIFO); // Read packet length (Fist byte in packet)

BytesRemaining = length; // length byte doesn't include the first byte in VPM

}

CC1120_ReadBurst(CC1120_FIFO, pData, RX_FIFO_THRESHOLD_SIZE); // Read the RxFIFO contents

BytesRemaining -= RX_FIFO_THRESHOLD_SIZE;

pData += RX_FIFO_THRESHOLD_SIZE;

}

// Case 2: End of packet detected (set by falling edge on GPIO2 - Set as GPIO2_CFG = 6)

else if (RxTxEndOfPacket)

{

RxTxEndOfPacket = FALSE;

if (!length) // Extract length.. DON'T include with data

{

length = CC1120_ReadRegister(CC1120_FIFO); // Read packet length from FIFO

BytesRemaining = length; // length byte doesn't include the first byte in VPM

}

// Process data from the two status bytes appended to the data

RxRssi =CC1120_ReadRegister(CC1120_FIFO); // Read remaining contents

RxLqi =CC1120_ReadRegister(CC1120_FIFO); // Read remaining contents

RxCrcOK = RxLqi & 0x80;

RxLqi &= 0x7F; // Keep 7 LSbits

if (!RxCrcOK) // MSBit is CRC

length =0; // Indicates a bad CRC == packet no good

break; // We're done!

}

if ((HAL_GetTick() - startTime) >= CC1120_RX_TIMEOUT_1S)

{

length = 0; // Timeout

break;

}

}

while(1);

return length;

}