Other Parts Discussed in Thread: SN74LVC1G3157

工具与软件:

尊敬的技术支持团队:

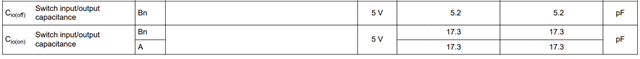

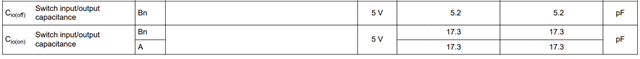

SN74LVC1G3157的以下电容 Cio (on)和 Cio (off)在哪里?介于哪里?

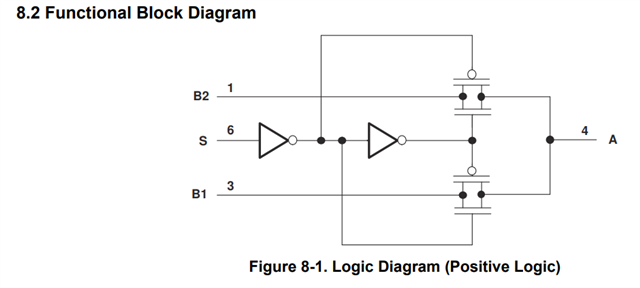

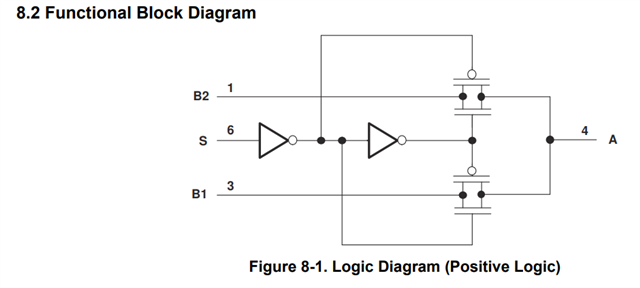

我想这三个地方是简化的,但我想知道它们是寄生的比例是多少。

Bn 引脚和 GND 之间・Ω

引脚和 GND 之间为・Ω

连接 Bn 的开关和之间・μ F (例如 FET 漏极和源极之间的电容)

如果可能、您能否在方框图中填写相应的器件?

最棒的餐厅

TTD

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: SN74LVC1G3157

工具与软件:

尊敬的技术支持团队:

SN74LVC1G3157的以下电容 Cio (on)和 Cio (off)在哪里?介于哪里?

我想这三个地方是简化的,但我想知道它们是寄生的比例是多少。

Bn 引脚和 GND 之间・Ω

引脚和 GND 之间为・Ω

连接 Bn 的开关和之间・μ F (例如 FET 漏极和源极之间的电容)

如果可能、您能否在方框图中填写相应的器件?

最棒的餐厅

TTD

您好、Akihisa、

通常、出于仿真目的、我们会说 C1和 C2各为1/2 CON。 对于1:1开关、这保持非常一致、但实际上、由于漏极侧的导体空间稍大、因此对于 x:1开关、您可能会在漏极侧看到更多的导体空间。 因此对于该器件、A 侧的 CON 电流会稍高。 例如、对于 a 为10pF、对于 b1为7pF。

源极和漏极的 COFF 相同。 因此、使用相同的等效模型时、C1和 C2将为5pF、而 RON 将具有非常大的阻抗。

谢谢!

Rami