Other Parts Discussed in Thread: LMKDB1202EVM, LMKDB1202, LMK3H0102

主题中讨论的其他器件: LMKDB1202、 LMK3H0102

工具/软件:

您好、

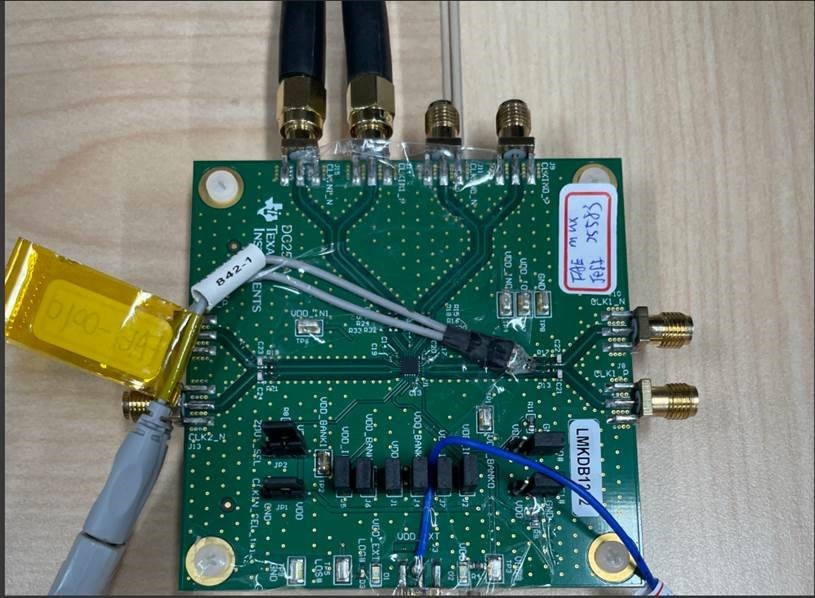

我们将 Clk1in P/ N 连接 到 clk 生成器 EVB 100 MHz、并 将 JP1切换到 H、 、但输出 clk1 P / N 无输出。

OE2#/OE1#/-> GND

CLKIN_SEL_tri/ZOUT_SEL -> VDD

是否遗漏了任何配置? 谢谢!

Jeff