请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:CD74HC4051-Q1 大家好,

我有一个需要您帮助的应用问题。

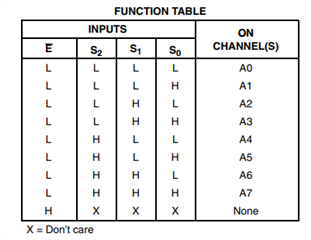

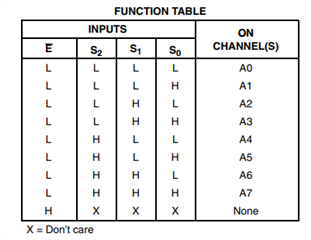

芯片通电后,S0 S1和S2的状态是什么? X是否表示高阻抗? 如果不是,会是什么?

如果在使用过程中将连接到S0的C2000的GPIO引脚设置为输入模式,会有什么影响?

期待您的回复~

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,

我有一个需要您帮助的应用问题。

芯片通电后,S0 S1和S2的状态是什么? X是否表示高阻抗? 如果不是,会是什么?

如果在使用过程中将连接到S0的C2000的GPIO引脚设置为输入模式,会有什么影响?

期待您的回复~

“X”表示允许高或低。

S0/S1/S2是高阻抗CMOS输入,不得浮动。 参见 [FAQ]慢速或浮动输入如何影响CMOS设备?

您好,Hangjie:

当/E设置为高时,所有信道都将具有高阻抗,并且无论S0,S1或S2引脚的状态如何,都不会有活动信道(在这种情况下,X是"不在乎")。

就每次开机的状态而言,我很难说。 如果您使用VCC来增加/E引脚,则它们将处于禁用状态。 否则,如果/E为低电平,则逻辑针脚上的电压可能未知,并且根据电路的条件,它可能会记录为高电压或低电压。 在这种情况下,最好使用上拉或下拉来确保逻辑引脚始终处于状态。

谢谢!

Bryan