尊敬的工程师:

系统具有两条 SPI 总线、其中单个 SPI (具有单独的 CS)上连接了50MHz 和75MHz 频率的三个器件。

当 SPI MISO 与多个从器件共享并基于 CS 时、SDO 将为三态。 系统将使用三个 CS、并在两个 ADC 之间共享、以同时对连接在两条独立 SPI 总线上的数据进行采样。

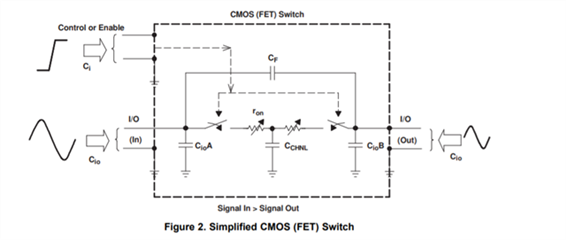

在 uC 端、我计划使用 TMUX136 (用于 CLK、MISO)作为缓冲器来连接端口 A (75MHz 时为1个器件)和端口 B (50MHz 时为2个器件)。 而 CS 将直接由 UC 驱动。

我的问题如下:

与多个从器件共享时、是否可以在50m 和75M 下运行 SPI (我们将保持低布线电容)

2.您是否建议使用更好的缓冲器将 SPI 总线拆分为两个、以便在每个总线上使用3个从器件?

3、每个端口上有两个负载时、能否将高达75MHz 的 TMUX136用于 SPI 接口?

我假设 TMUX136是透明的、那么端口 A 和 B 的容性负载将如何影响 COM 端口的输入 Con = 2pf。 uC 将在 Con Con =2pf Capciatance 加上迹线寄生效应??

或者、当选择端口 A 时、UC 将在选择端口 B 时看到 Ccon+Cslave1+寄生效应。总负载将=Ccon+Cslave2+Cslace3+寄 生效应?

感谢您的支持