请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TS5MP645 尊敬的先生/女士:

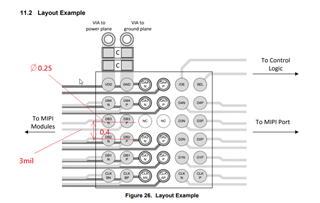

我想请求有关 TS5MP645布局的支持。 在数据表中、显示了布局示例:

这意味着数据+/-跟踪是差动的。 迹线。 但是、我的设计是12层 PCB。 为了满足 MIPI DIFF 100欧姆请求、 顶层的布线宽度/空间为3mil/6.5mil。 TS5MP645焊球直径为0.25mm、间距为0.4mm。 这意味着两个焊盘之间的间隙为0.15mm = 5.9mil。 然后、MIPI 走线和 TS5MP645之间的距离为(5.9-3)/2 = 1.45mil…… 它太小、无法制造。 您有其他布局示例吗? BTW、最大值是多少。 MIPI 模块和 TS5MP645之间的长度,以避免大损耗?

谢谢。