请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74CBTLV3253 您好,

是 Inventec 服务器团队的 Jon。

现在、我们发现症状需要您的支持。

我们的项目使用 TI SN74CBTLV3253、发现了一些异常症状。

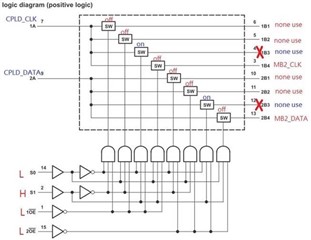

如下面的 pig1中的规格逻辑图所示、

当 S1 = H (3.3V)、S0 = L (0V)时、强制开启两个内部 SWS、1A = 1B3、2A = 2B3。

我们发现1A 从1B4拾取一些噪声、而2A 从2B4拾取一些噪声、例如下面的波形捕获。 上面150mVp-p 附近的噪声作为鸽子2。

它是否合理?为什么?

或其他解决方案可以降低噪声。 请提供建议。